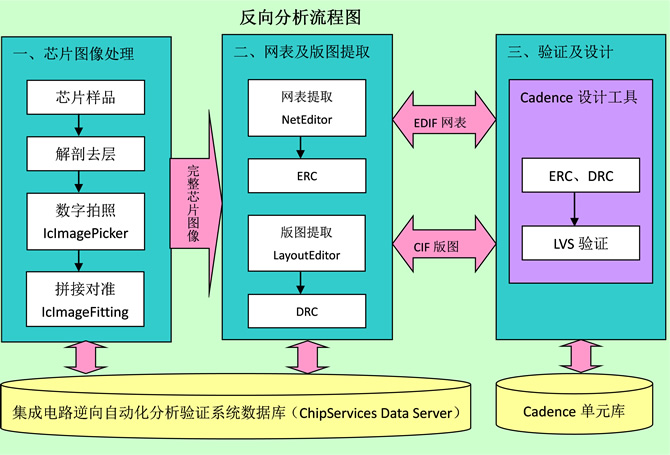

IC competitiveness analysis flow chart |

In the integrated circuit industry, chip competitiveness analysis, also known as chip competitor analysis, is a way to obtain design and process information of competitors through chip reverse analysis or reverse analysis of already listed chip products, in order to enhance the competitiveness of one's own products. So, what is the process of analyzing the competitiveness of integrated circuits? How are the various processes carried out? The following diagram illustrates the entire process of reverse development of integrated circuits, including each step and the complete workflow. |

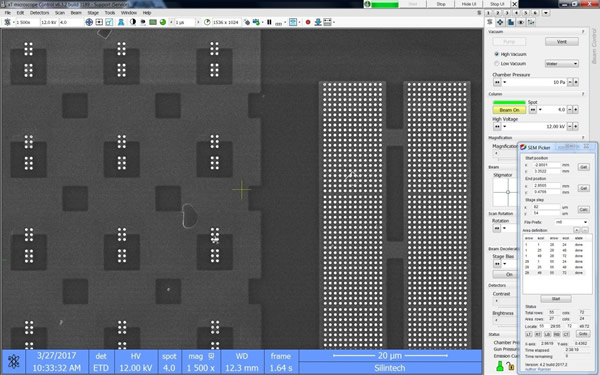

1、Chip de-cap and de-layer

|

The chip is coated with the package. Therefore, package removal is the first step for inverse engineering. Firstly, place the target chip in the container filled with concentrated sulfuric acid, and put on the container cover, which can’t be fully closed, so the gas can flow out. Heat the concentrated sulfuric acid in the container to burning status (about 300 Celsius). Sprinkle some baking powder around the container bottom – to prevent the splashed sulfuric acid solution and the spilled sulfuric acid gas. |

2、Chip imaging

|

Poly Diagram under electron microscope 2000 X 4 amplification factor |

Perform microscopic image acquisition for chip sample layer by layer on the microscopic image automatic acquisition platform. Different from the inverse design of measuring 3D object or curved surface, measuring IC chip is simply on the surface. You just need to place the chip on the right position, adjust the focus, and select the amplification factor, making the chip surface clearly visible on the lens and the microscope. Finally, press shutter button to finish acquisition of one microscopic image. A circuit layer may require stitching multiple images, which depends on the circuit scale and amplification factor. And multiple circuit layers require alignment after stitching. Some automatic microscopic image stitching software is used for stitching and alignment operation. For example, the microscopic image automatic acquisition platform is set with 100 amplification factor. Then you may adjust the line width of 0.1um to 0.1mm. It indicates it is enough for the 0.09um IC chip based on the most advanced process. |

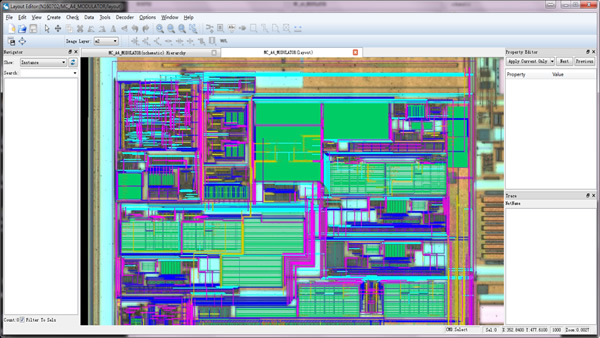

3、Schematic extraction

|

IC is composed of multiple layers, each of which is confirmed with photo mask by photoetching. The geometric diagram on the photo mask used for IC manufacturing is the layout, which is the corresponding physical layer of the IC. The mainstreaming circuit schematic analysis system has the powerful functions of multi-layer microscopic image view, circuit unit symbol design, automatic and interactive extraction of circuit schematic and circuit schematic editing. The layout analysis system can finish the automatic extraction of multi-layer layout profile, full-functional layout editing, automatic identification, extraction, and verification of embedded software code, count and extraction of design rules. |

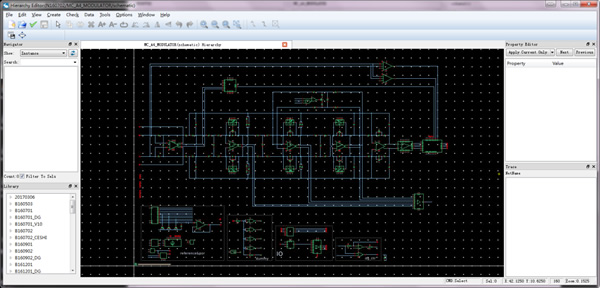

4、Circuit extraction and arrangement

|

The digital circuits need to be classified based on the schematic types, such as NAND gate, NOR gate, and trigger. The schematic of the same type doesn’t have to be analyzed for several times. The extracted circuits are sketched by using the circuit drawing software (ViewWork, Laker, Cadence, and etc.), which are arranged from the easy-to-understand items. Therefore, others can understand the functions you extract from the circuit. The speed of circuit extraction totally depends on the experience of the operation personnel. |

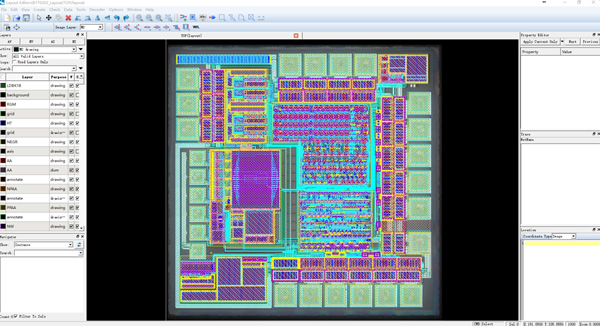

5、Circuit analysis and sorting

|

The extracted circuits are converted into circuit drawings, which are also entered with geometric parameters (MOS is the width-length ratio). Through your analysis, the circuit functions are clear and the circuit connections are correct. |

6、Simulation verification and circuit adjustment

|

View, query, edit, debug and simulate the entered circuit schematics. Analyze the circuit principles, adjust the circuit parameters, and observe the output wave under certain excitatory input, so as to verify the design logic. Perform simulation verification for the target netlist to be extracted, compare it with the pre-simulation results, export GDS file from layout, and tape out (submit the design data to the manufacturer). |