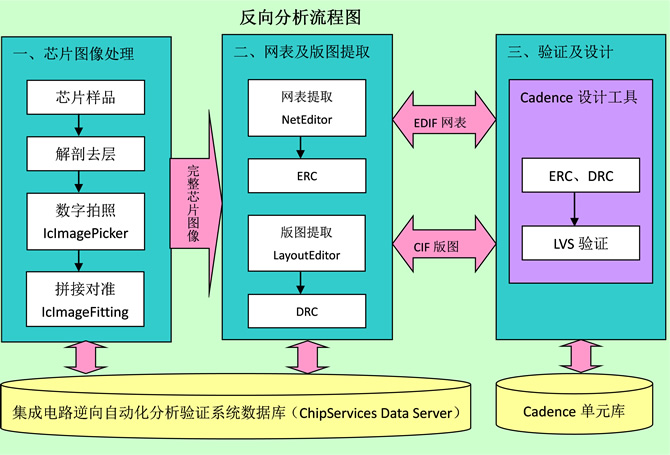

IC競爭力分析流程圖 |

在積體電路行業,對晶片進行競爭力分析,是提高產品研發效率,縮短產品上市週期的一種有效的方式。 那麼,積體電路的競爭力分析是怎樣的一個流程?其各道工序又如何進行? 下面這張圖就說明了積體電路反向開發的各道工序、完整流程的全過程。 |

1、晶片開蓋去層

|

晶片是自帶馬甲的,那就是晶片的封裝。所以,反向工程的第一步就是要剖開晶片。首先把要拆解的晶片放置在裝了濃硫酸的容器裡,容器需要蓋住,但不能嚴實,這樣裡面的氣體才能漫溢出來。把容器裡的濃硫酸加熱到沸騰(大約 300 攝氏度),在瓶底的周圍鋪上蘇打粉——用來預防意外飛濺出來的硫酸液和冒出來的硫酸氣體。 |

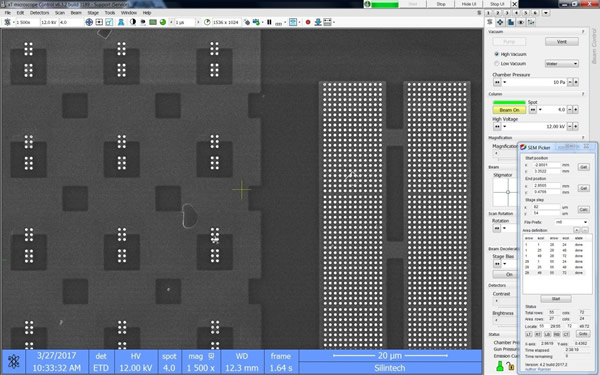

2、晶片拍照

|

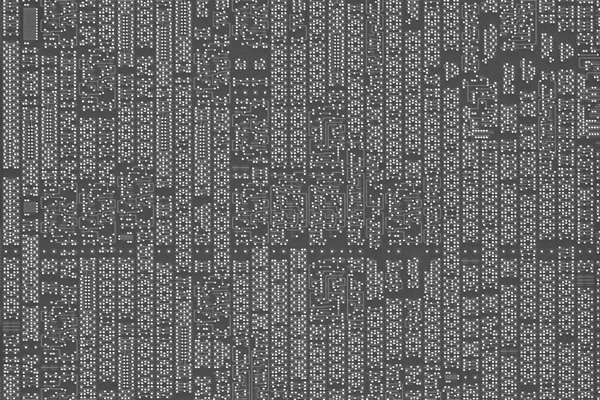

電鏡2000x4放大倍數下的poly圖 |

在顯微圖像自動採集平臺上逐層對晶片樣品進行顯微圖像採集。與測量三維實體或曲面的逆向設計不同,測量積體電路晶片純屬表面文章:放好晶片位置、對對焦、選好放大倍數,使晶片表面在鏡頭中和顯示器上清晰可見後,按下拍照按鈕便可完成一幅顯微圖像的採集。 取決於電路的規模和放大倍數,一層電路可能需要在拍攝多幅圖像後進行拼湊,多層電路需要在拼湊後對準,有顯微圖像自動拼湊軟體用於進行拼湊和對準操作。 例如,顯微圖像自動採集平臺的放大倍數為1000倍,則可將0.1um線條的放大至0.1mm的寬度。這意味著它已足以對付目前採用最先進工藝製作的0.09um積體電路晶片。 |

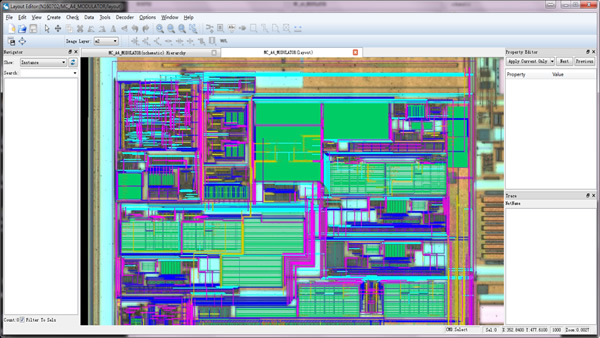

3、提圖

|

積體電路由多層組成,每層用光刻工藝由光掩膜加以確定。製造積體電路時用的掩膜上的幾何圖形就是版圖,版圖是積體電路對應的實體層。 主流的電路原理圖分析系統具有多層顯微圖像流覽、電路單元符號設計、電路原理圖自動和互動式分析提取以及電路原理圖編輯等強大功能,版圖分析系統則可完成多層版圖輪廓自動提取、全功能版圖編輯、嵌入軟體代碼自動識別、提取、校驗以及設計規則的統計和提取。 |

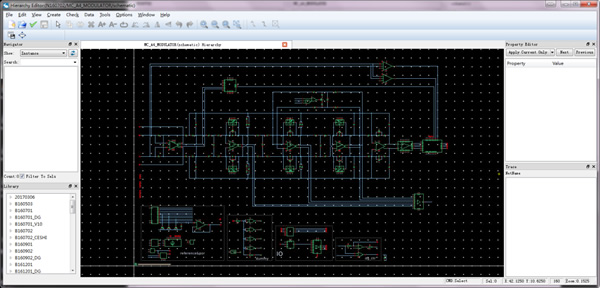

4、電路提取與整理

|

數位電路需要歸併同類圖形,例如反及閘、反或閘、觸發器等,同樣的圖形不要分析多次。 提出的電路用電路繪製軟體繪出(ViewWork、Laker、Cadence等),按照易於理解的電路佈置,使其他人員也能看出你提取電路的功能,提取電路的速度完全由提圖人員經驗水準確定。 |

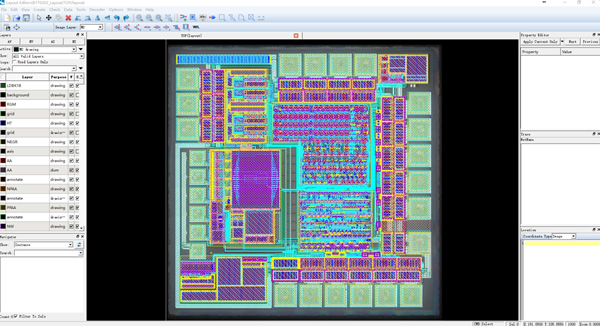

5、電路分析與整理

|

提取出的電路整理成電路圖,並輸入幾何參數(MOS為寬長比)。通過你的分析,電路功能明確,電路連接無誤。 |

6、模擬驗證與電路調整

|

對輸入的電路原理圖進行流覽、查詢、編輯、調試與模擬。分析電路原理,調節電路參數,並在一定的激勵輸入下觀測輸出波形,以驗證設計的邏輯正確性。 要對提取的網表作模擬驗證,並與前仿結果對比,版圖匯出GDS檔,Tape out(將設計資料轉交給製造方)。。 |