芯聯成自主研發的BunnyGS®系統,是一款專為集成電路競爭力分析和知識產權分析定製的EDA工具軟件,融合了圖像處理、AI算法、雲計算等關鍵核心技術,高度集成完備的版圖和原理圖編輯、數字電路信號流分析和自動布局布線等子系統,強大的電路分析和處理能力,能滿足客戶對超大規模IC項目的分析需求,並提供可定製化的集成電路分析解決方案。

芯聯成在與客戶合作交流的過程中,收集了客戶的需求和建議,現已將BunnyGS®軟件更新到V1.8.4版本,該版本合入了一些關鍵的技術和算法,主要更新如下:

(1) 兼容Cadence PCell,支持PCell繪製版圖;

(2) 新增數字電路中組合邏輯的BOOL仿真功能;

(3) 全新EDIF格式輸出算法,有效取代人工替換PDK單元;

(4) BunnyGS®系統與仿真驗證軟件無縫對接。

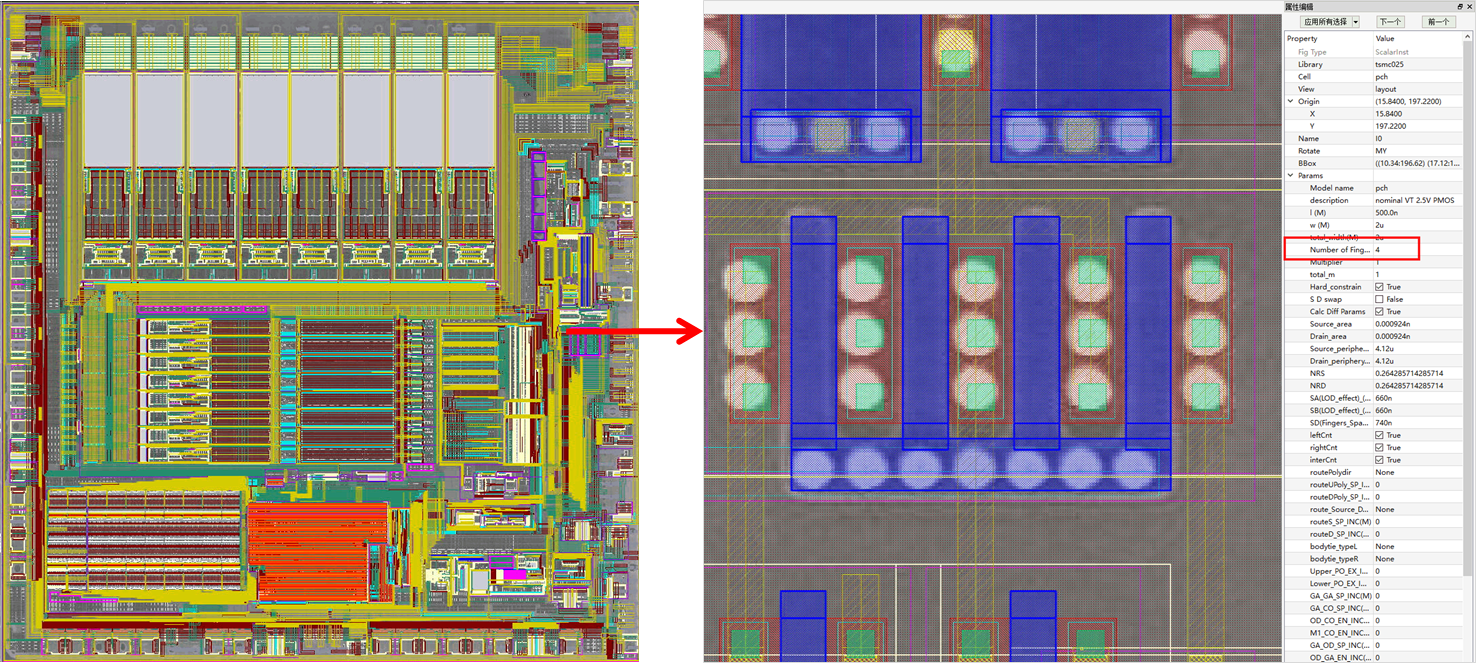

1.1. 兼容Cadence PCell,支持PCell繪製版圖

Cadence PCell工藝庫是用SKILL語言開發的,其他EDA軟件無法原生態支持。BunnyGS®軟件實現了一種能兼容Cadence PCell工藝庫的方法,支持使用PCell繪製版圖,芯聯成自研的sltPcell程序,能支持CSMC、DB、HHNEC、SMIC、TSMC等常見工藝庫,提高了Cadence PCell工藝庫兼容的靈活性。

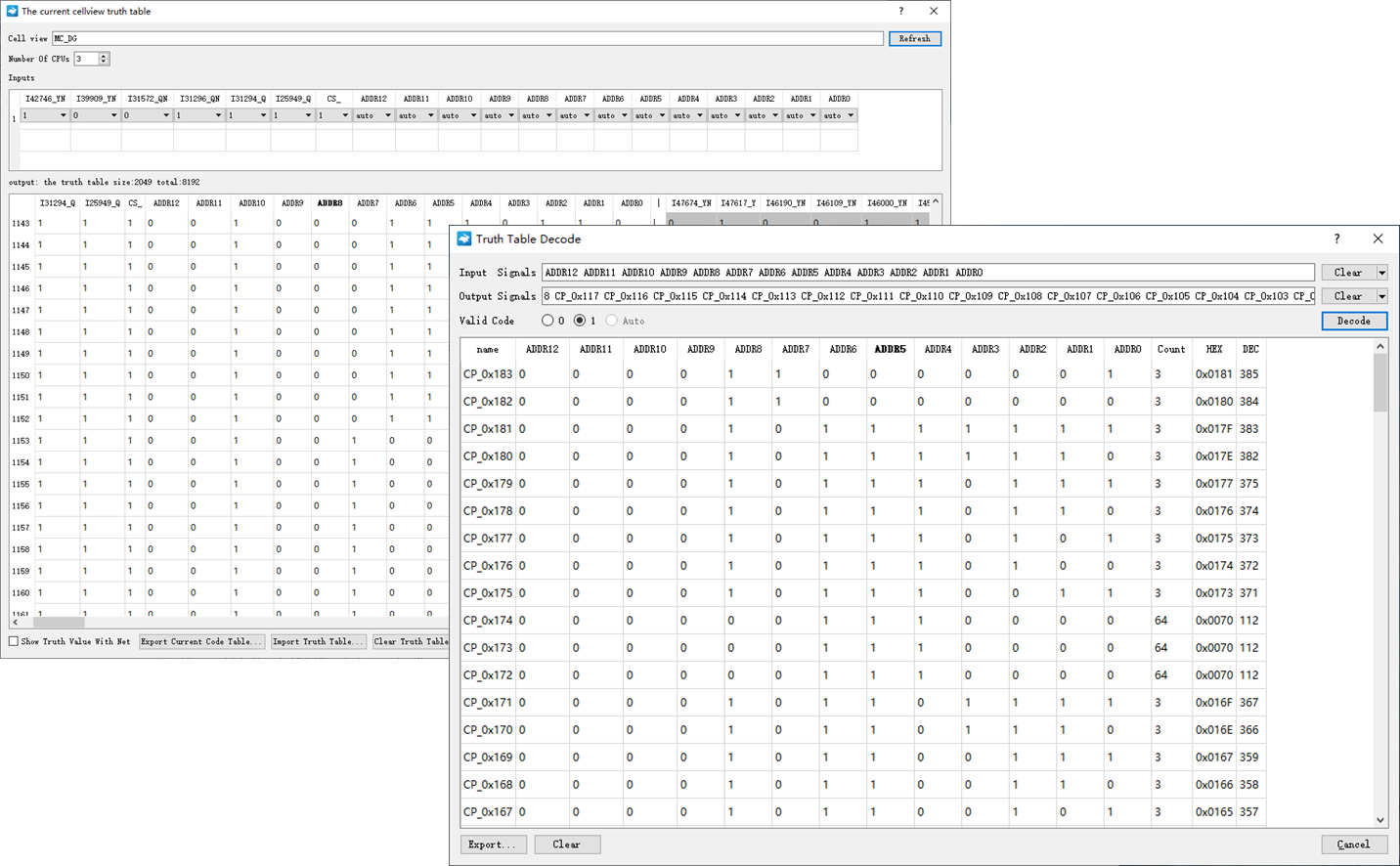

1.2. 新增數字電路中組合邏輯的BOOL仿真功能

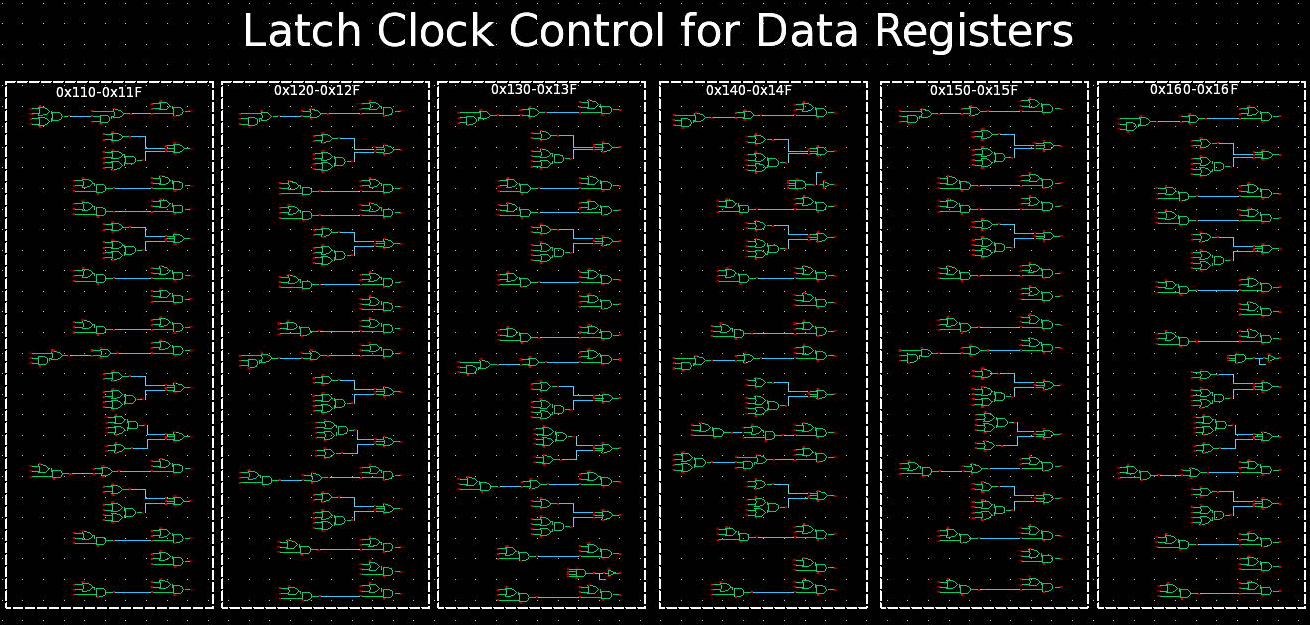

BunnyGS®軟件新增了數字電路中組合邏輯的BOOL仿真功能,目前最大支持13位數據輸入,即可一次完成8192次遍歷運算。同時,軟件支持對運算結果進行在線解碼,用戶可根據需要對輸入輸出信號進行排序和選擇,在選擇有效值後可直接得到解碼結果。

該功能常用於分析內部線網關系復雜、實例數量較大的電路模塊,如譯碼(器)電路、算法實現電路等,在使用時可忽略其內部復雜的結構,一次完成從輸入到輸出的邏輯映射,高效地完成電路分析。例如在分析以太網通訊芯片、距離傳感器芯片等具有復雜寄存器映射的芯片時,使用該功能通過一次仿真即幫助工程師得到芯片的完整寄存器映射,數據流向分析因此更快更準。

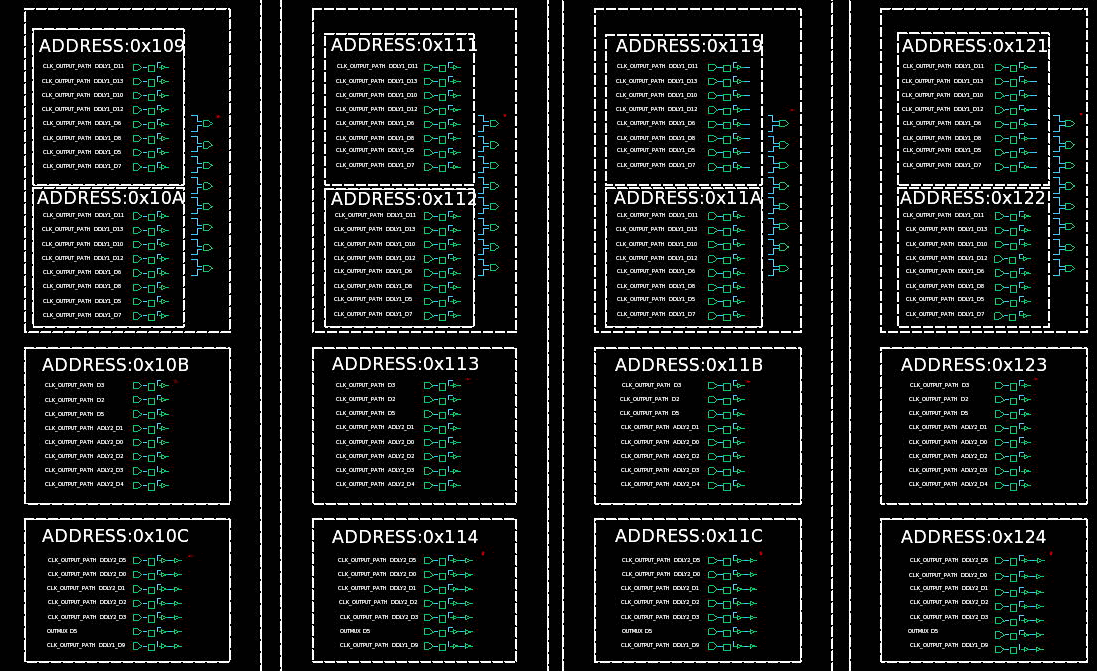

1.3. 全新EDIF格式輸出算法,有效取代人工替換PDK單元

工程師設計好的電路有時需替換工藝庫,不同工藝庫之間的器件種類、數量及參數名稱和約束等都不相同,傳統的替換工藝庫的方法是在視圖上逐一修改器件類型。項目的器件數量巨大,逐個修改必然會帶來難以估計的工作量,同時器件參數存在映射或約束關系,無法直接修改。

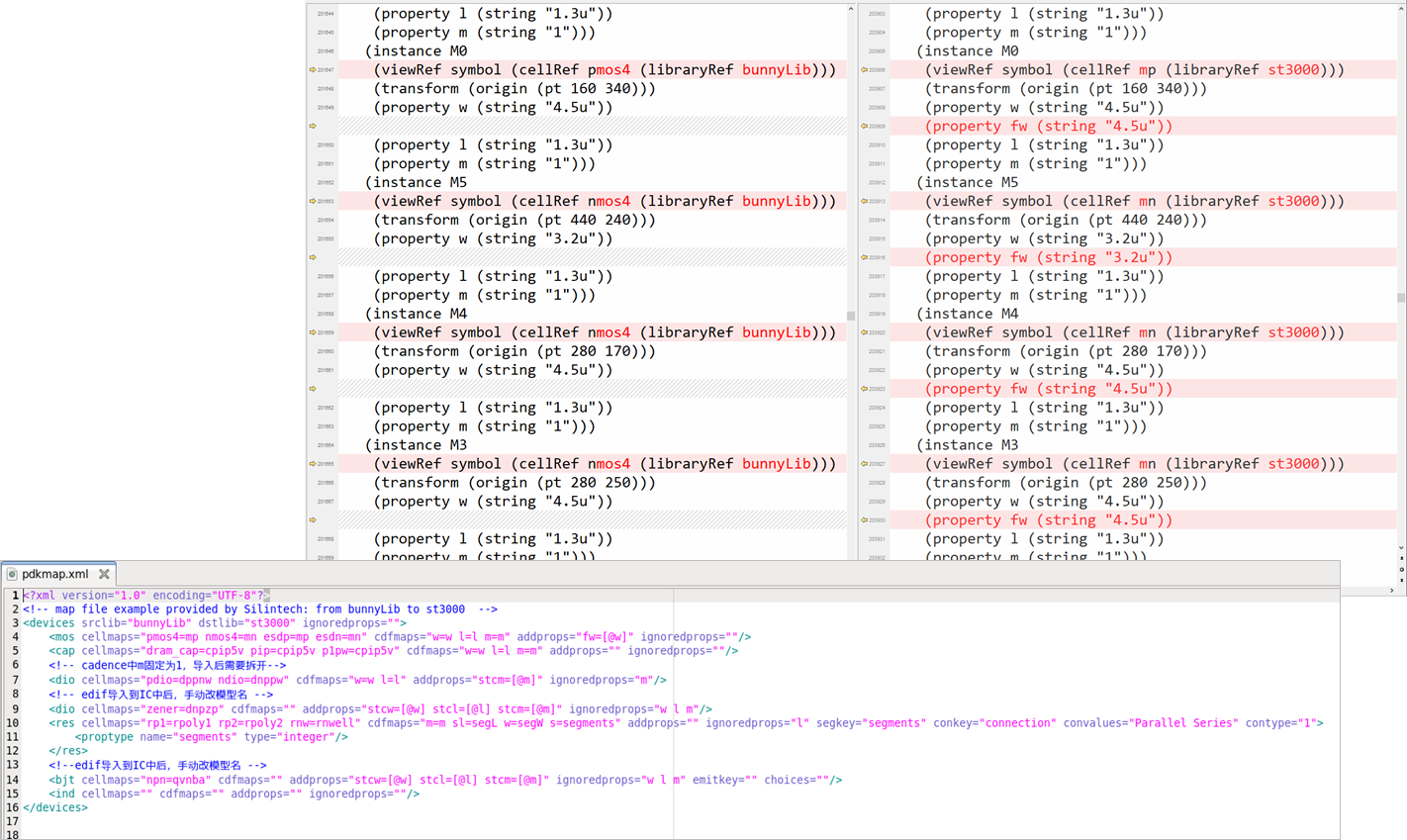

芯聯成開發了一種高PDK兼容度的EDIF格式輸出算法,通過器件庫和PDK庫的器件名稱和參數映射關系配置pdkmap.xml文件,在導出EDIF時,軟件自動將BunnyGS®提取的器件轉換為相應的PDK器件,同時更新器件的參數。使用高PDK兼容度的EDIF格式輸出算法後,工程師能通過導出的EDIF文件準確、高效地替換PDK庫,為高效、高質量地交付項目提供了有力支撐。

pdkmap.xml文件示例

1.4. BunnyGS®系統與仿真驗證軟件無縫對接

大規模數字電路仿真驗證中,需要導出模塊的verilog文件。BunnyGS®軟件支持分類別導出verilog,可以將所有基本單元的functional視圖導入到同一文件中,宏模塊導入到一個文件中。也可以將所有基本單元的functional視圖導入到同一文件中,不同宏模塊導入到不同文件中。將這些verilog文件導入到數字仿真軟件進行仿真驗證。

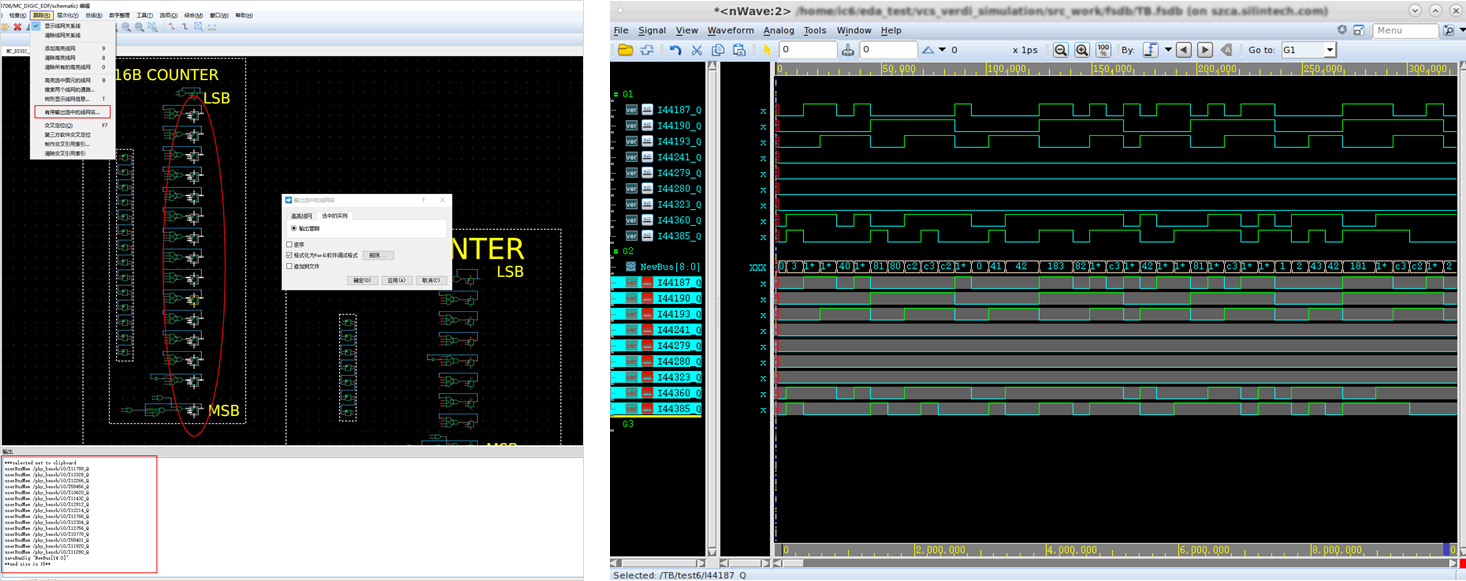

常用的數字仿真軟件有Synopsys公司的VCS和Verdi、Cadence公司的 ncverilog、Mentor公司的modelsim。Verdi等軟件的界面顯示的實例是無序的,沒有使用到規則的實例位置和有序的線網關系。

在進行驗證時,通常需要使用有序的信號或能快速地找到對應的信號。BunnyGS®軟件新增了格式化輸出線網名功能,對於整理好的電路,可以將有序的信號格式化為Verdi軟件調試格式輸出,減少了復雜和繁瑣的工作,方便工程師調試和跟蹤信號,讓工程師的工作重心落到驗證上。