BunnyGS® is a custom EDA software especially developed for IC competitive analysis and Intellectual property analysis. It incorporates core technologies, such as image processing, AI algorithms and cloud computing. It has complete tools on layout and schematic editing, quick search on datapath flow, automatic placement and routing for digital circuit sorting. With powerful processing and analysis capabilities, BunnyGS® not only can meet customer's demand for VLSI circuit analysis, but also can provide customizable solutions.

The BunnyGS® software has been updated to VERSION V1.8.4, which incorporates some key technologies and algorithms. The main updates are as follows:

(1) Compatible with Cadence PCell, support PCell layout;

(2) BOOL simulation of combinatorial logic in digital circuit;

(3) New EDIF format output algorithm, effectively replace manual replacement of PDK cells;

(4) BunnyGS® system seamlessly integrates with simulation verification software.

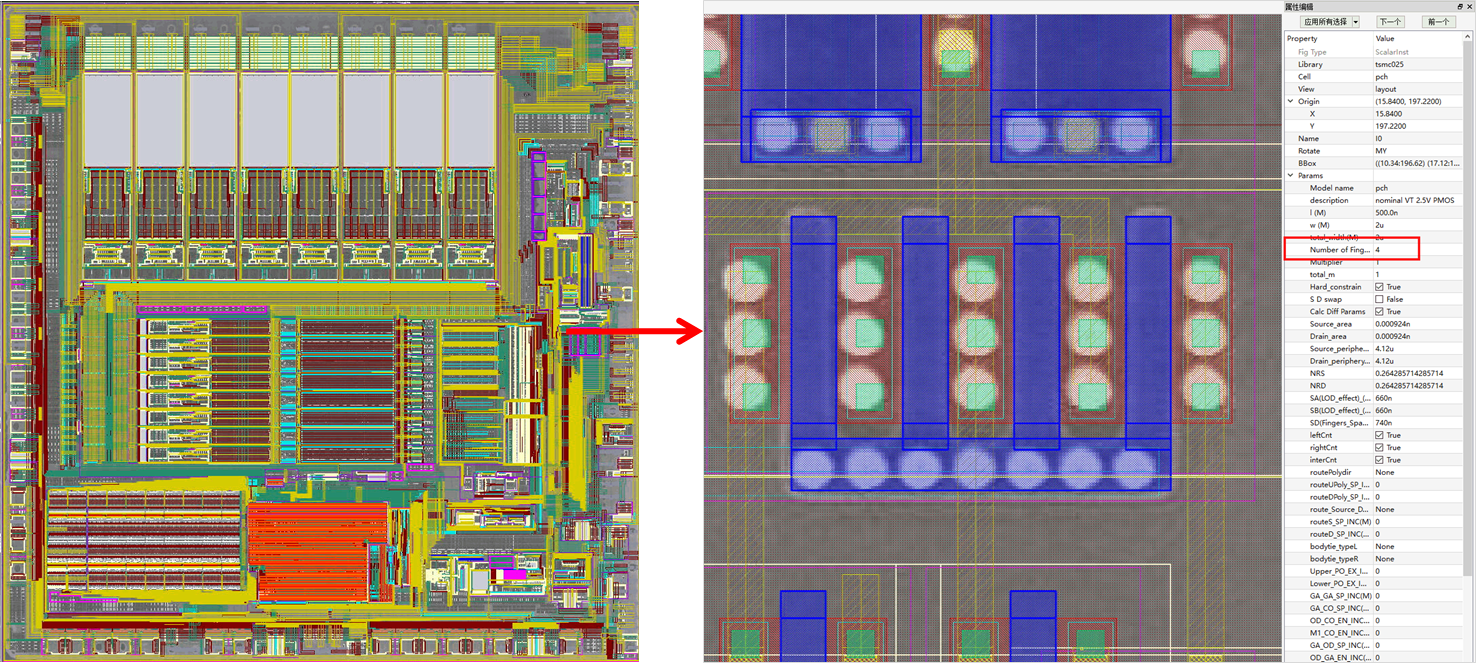

1.1.Compatible with Cadence PCell, support PCell mapping

Cadence PCell process library is developed with SKILL language, which is not supported by other EDA software. BunnyGS® software implements a method compatible with Cadence PCell process library. It supports the use of PCell to draw layout .The SltPcell program developed by Silintech, can support CSMC, DB, HHNEC, SMIC, TSMC and other common process libraries, improve the flexibility of Cadence PCell process library compatibility.

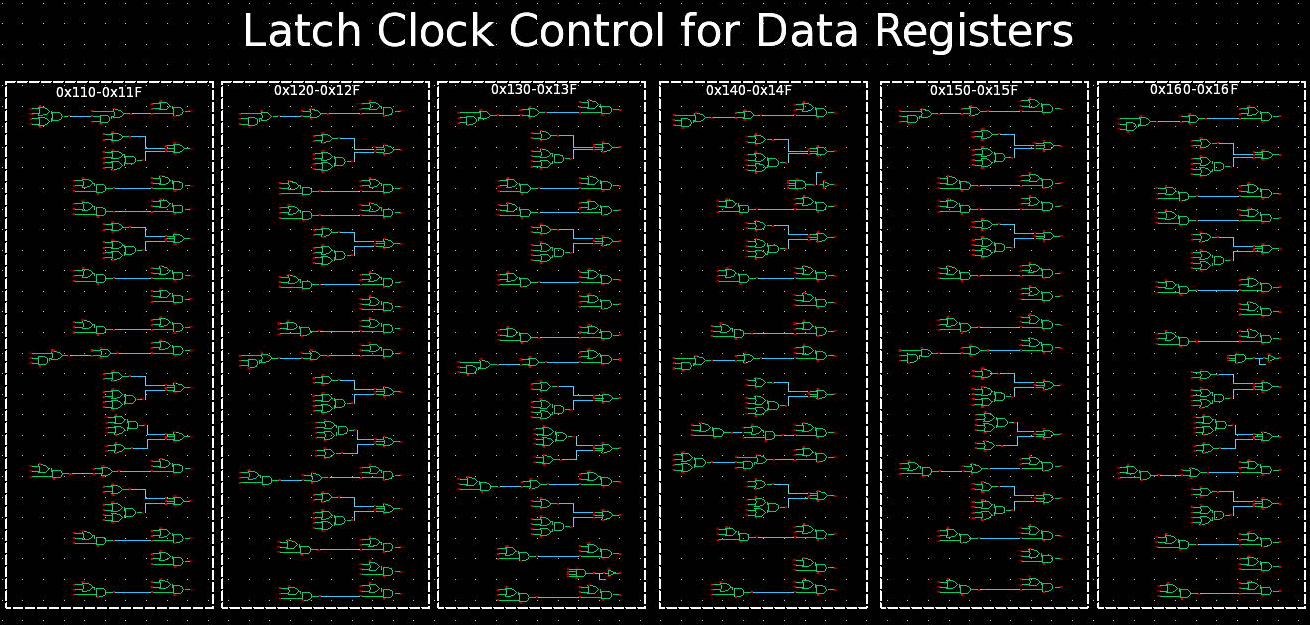

1.2. BOOL simulation of combinatorial logic in digital circuit

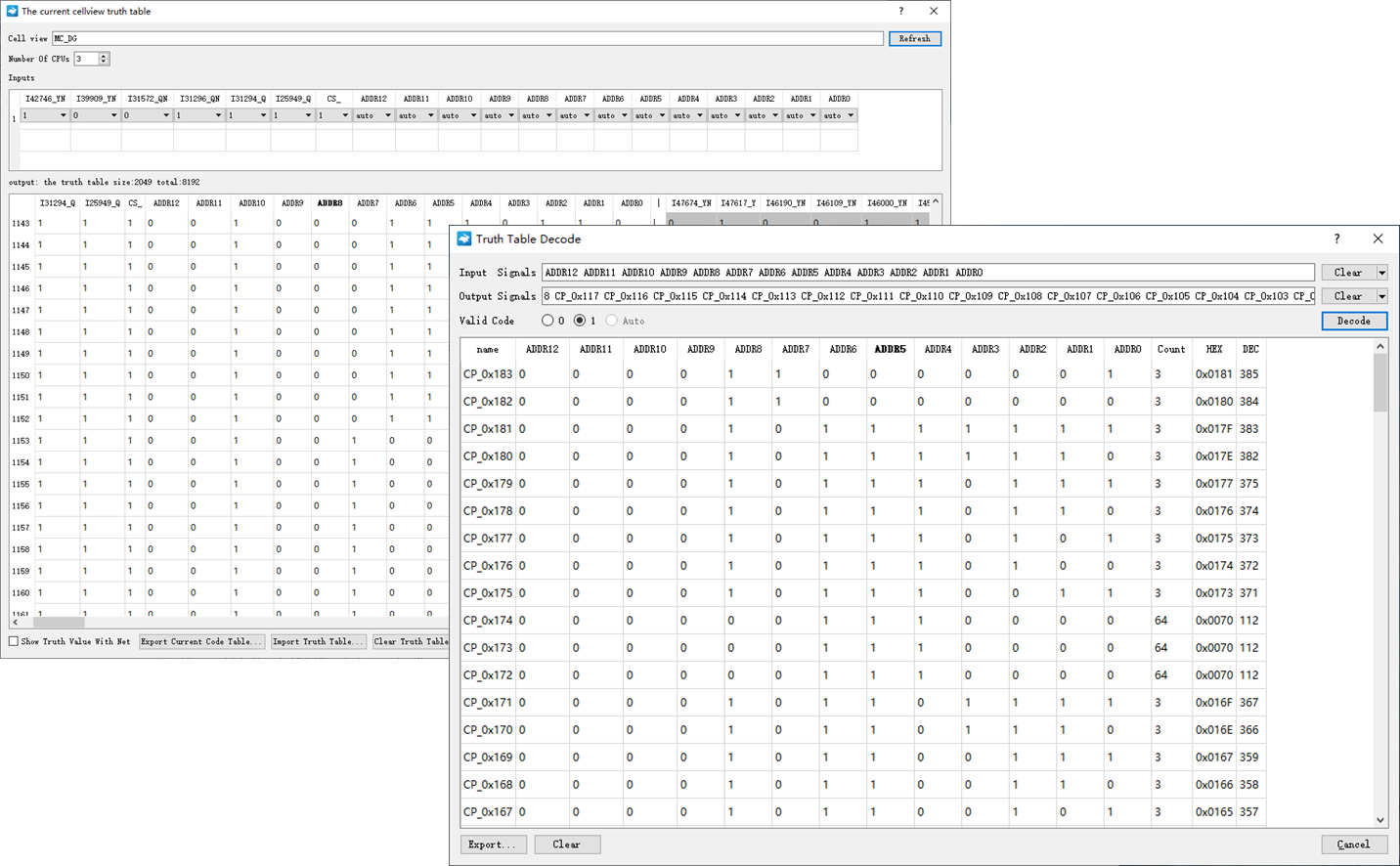

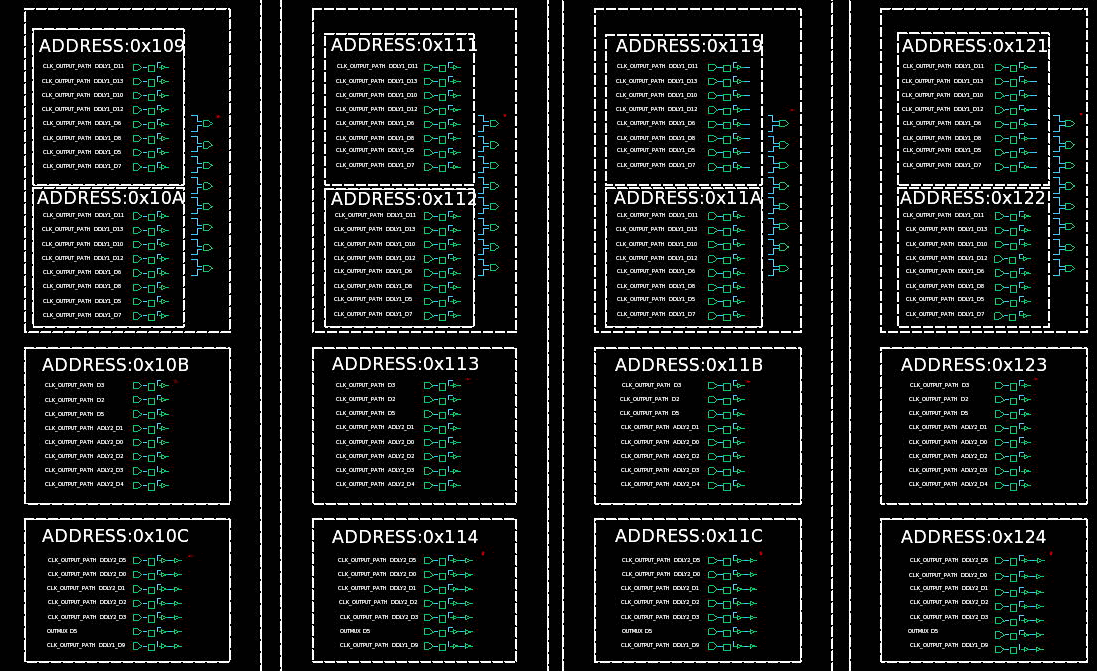

BunnyGS® software has added a BOOL simulation function for combinational logic in digital circuits, which supports up to 13 bits of data input and can perform 8192 traversals at a time. At the same time, the software supports online decoding of the operation results. Users can sort and select the input and output signals according to their needs. After selecting effective values, the decoding results can be directly obtained.

This function is often used to analyze circuit modules with complex internal circuit net relations and large number of instances, such as decoder circuit, algorithm implementation circuit, etc. It can ignore its complex internal structure, complete the logical mapping from input to output at one time, and efficiently complete circuit analysis. For example, when analyzing Ethernet communication chip, distance sensor chip and other chips with complex register mapping, this function can help engineers get the complete register mapping of the chip through one simulation, so that the data flow analysis is faster and more accurate.

1.3. New EDIF format output algorithm, effectively replace manual replacement of PDK cells

After circuit designed by engineers, the circuit library sometimes needs to be replaced with different process libraries. Device types, quantity, parameter names and constraints are different among different process libraries.The traditional way to replace the process library is to modify the device type one by one on the view.However, the number of devices in the project is huge, individual modifications are bound to bring about an incalculable amount of work,at the same time, device parameters can not be directily modified due to mapping or constraint relations.

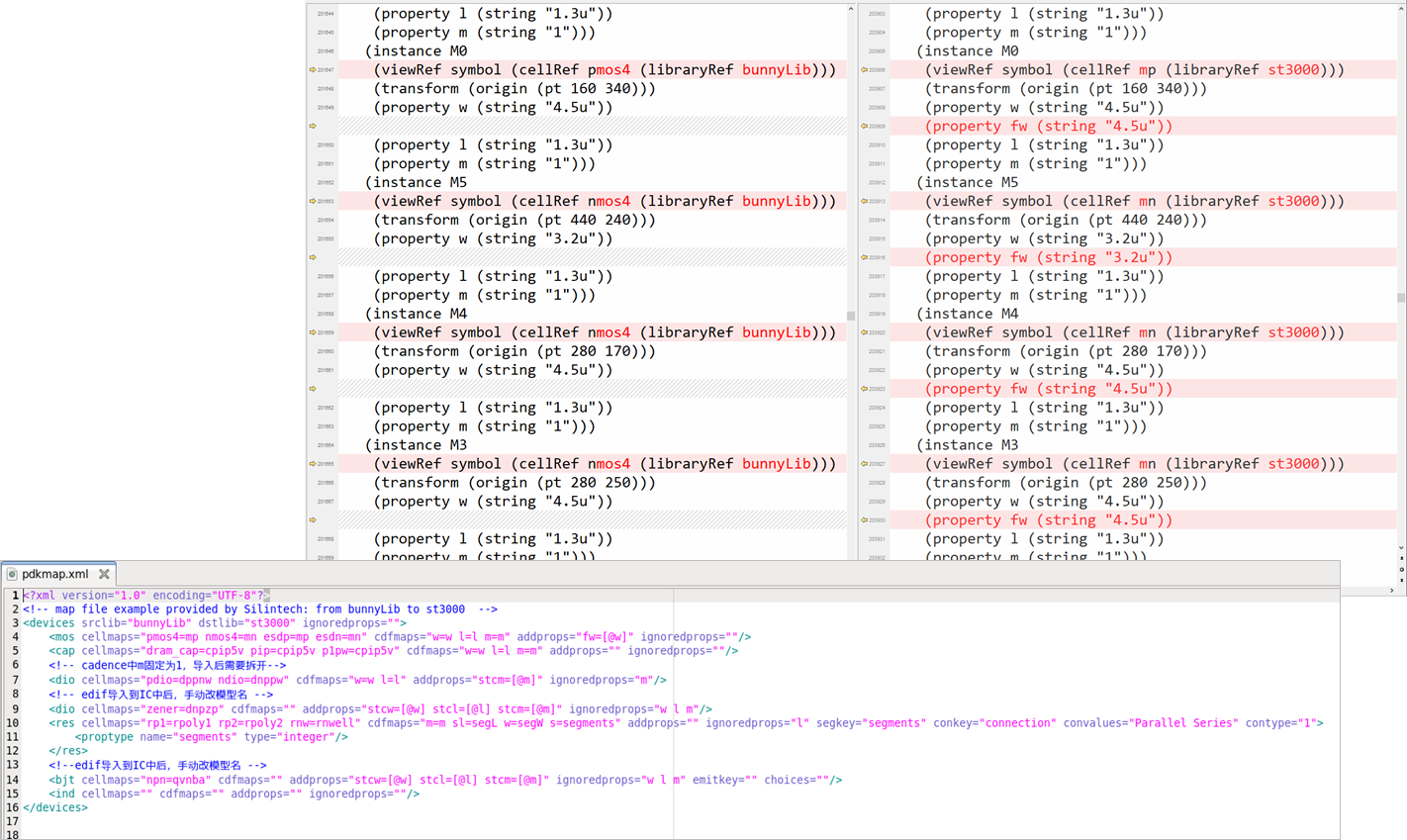

Silintech has developed an output algorithm for EDIF format with high PDK compatibility. The pdkmap.xml file is configured by device name and parameter mapping between device library and PDK library. When EDIF is exported, the devices extracted by BunnyGS® are automatically converted into PDK devices and meanwhile the parameters of the devices are updated. By using the output algorithm in EDIF format with high PDK compatibility, engineers can replace The PDK library accurately and efficiently by exporting EDIF files, which provides a strong support for efficient and high-quality project delivery.

Example of pdkmap.xml file

1.4. BunnyGS® system seamlessly integrates with simulation verification software

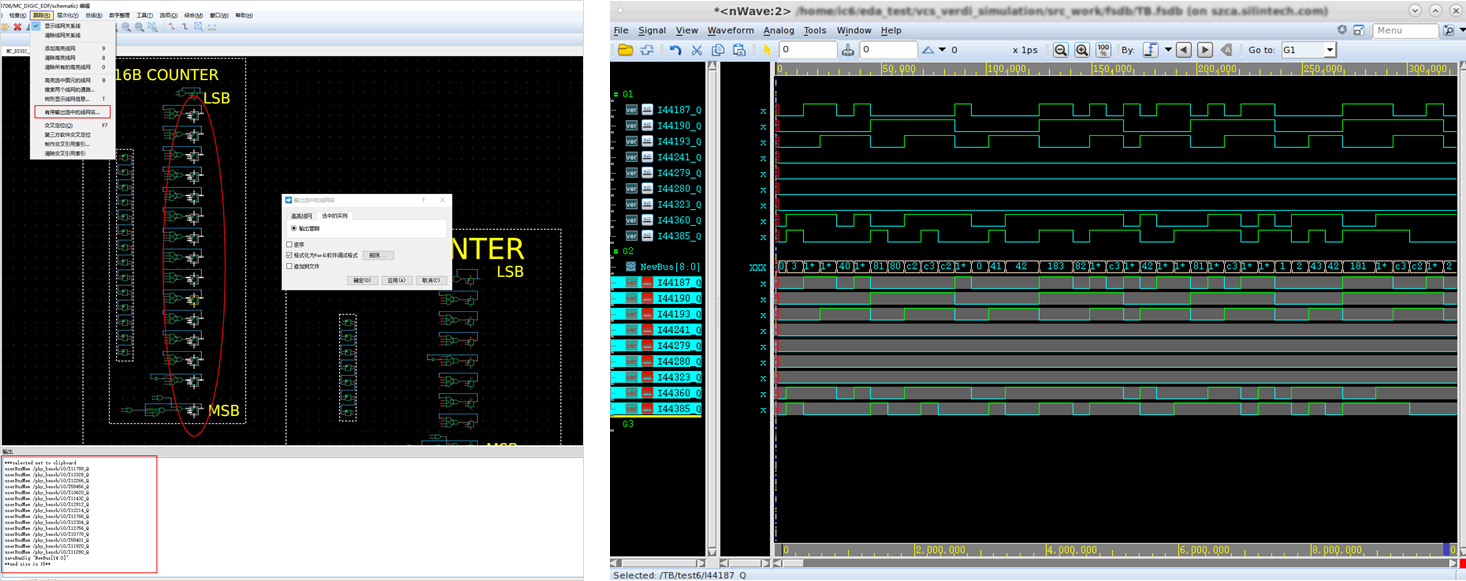

Verilog files of modules need to be exported in large scale digital circuit simulation verification. BunnyGS® supports category export verilog. You can import the functional view of all base cells into the same file, and import different macro modules into different files. And these Verilog files can be imported into the digital simulation software for simulation verification.

The commonly used digital simulation software includes VCS and Verdi of Synopsys, NCVerilog of Cadence, and ModelSim of Mentor.The instances and circuit net relations displayed in Verdi and other softwares are irregular and disordered.

In verification, it is usually necessary to use ordered signals or to find corresponding signals quickly. BunnyGS® has added the function of formatted outputting circuit net names, and it can format ordered signals into Verdi software debugging formats for output in already organized circuits. which reduces the complexity and tedious work and is much more convienient for engineers to debug and track signals, so that they can focus on verification.