芯联成自主研发的BunnyGS®系统,是一款专为集成电路竞争力分析和知识产权分析定制的EDA工具软件,融合了图像处理、AI算法、云计算等关键核心技术,高度集成完备的版图和原理图编辑、数字电路信号流分析和自动布局布线等子系统,强大的电路分析和处理能力,能满足客户对超大规模IC项目的分析需求,并提供可定制化的集成电路分析解决方案。

芯联成在与客户合作交流的过程中,收集了客户的需求和建议,现已将BunnyGS®软件更新到V1.8.4版本,该版本合入了一些关键的技术和算法,主要更新如下:

(1) 兼容Cadence PCell,支持PCell绘制版图;

(2) 新增数字电路中组合逻辑的BOOL仿真功能;

(3) 全新EDIF格式输出算法,有效取代人工替换PDK单元;

(4) BunnyGS®系统与仿真验证软件无缝对接。

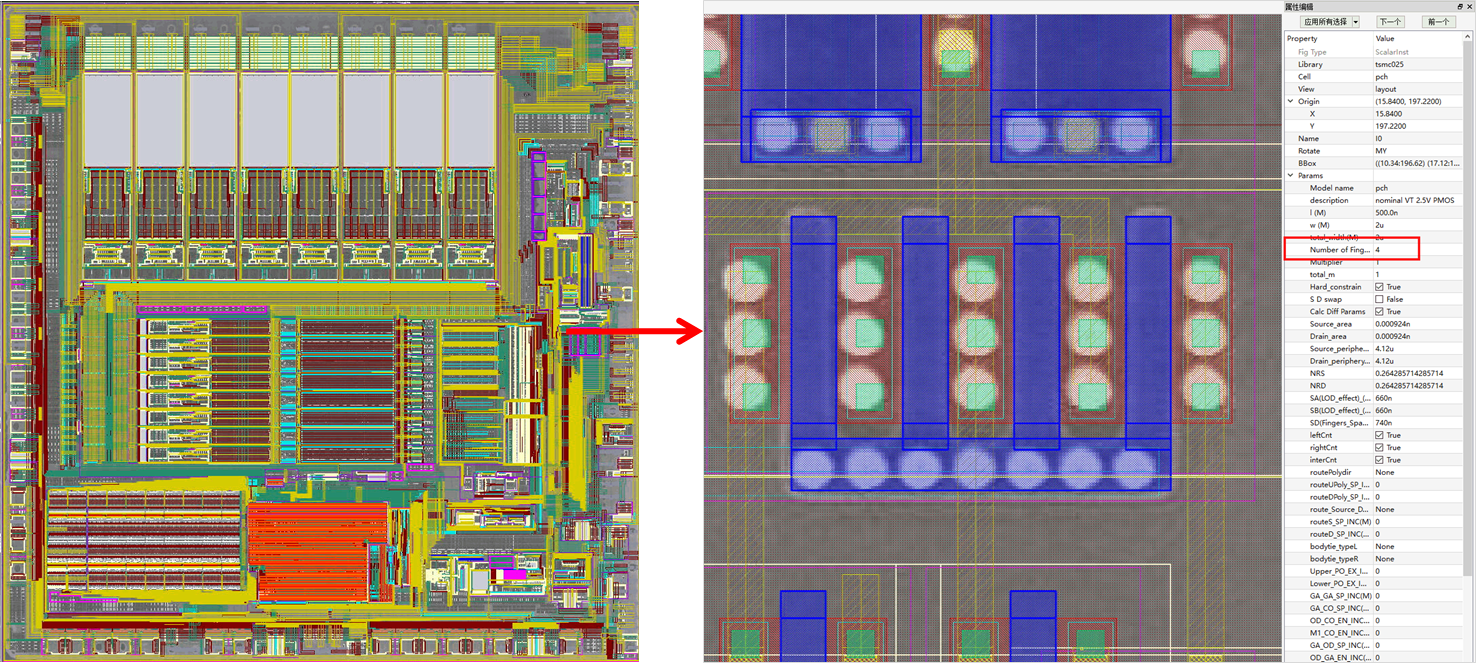

1.1. 兼容Cadence PCell,支持PCell绘制版图

Cadence PCell工艺库是用SKILL语言开发的,其他EDA软件无法原生态支持。BunnyGS®软件实现了一种能兼容Cadence PCell工艺库的方法,支持使用PCell绘制版图,芯联成自研的sltPcell程序,能支持CSMC、DB、HHNEC、SMIC、TSMC等常见工艺库,提高了Cadence PCell工艺库兼容的灵活性。

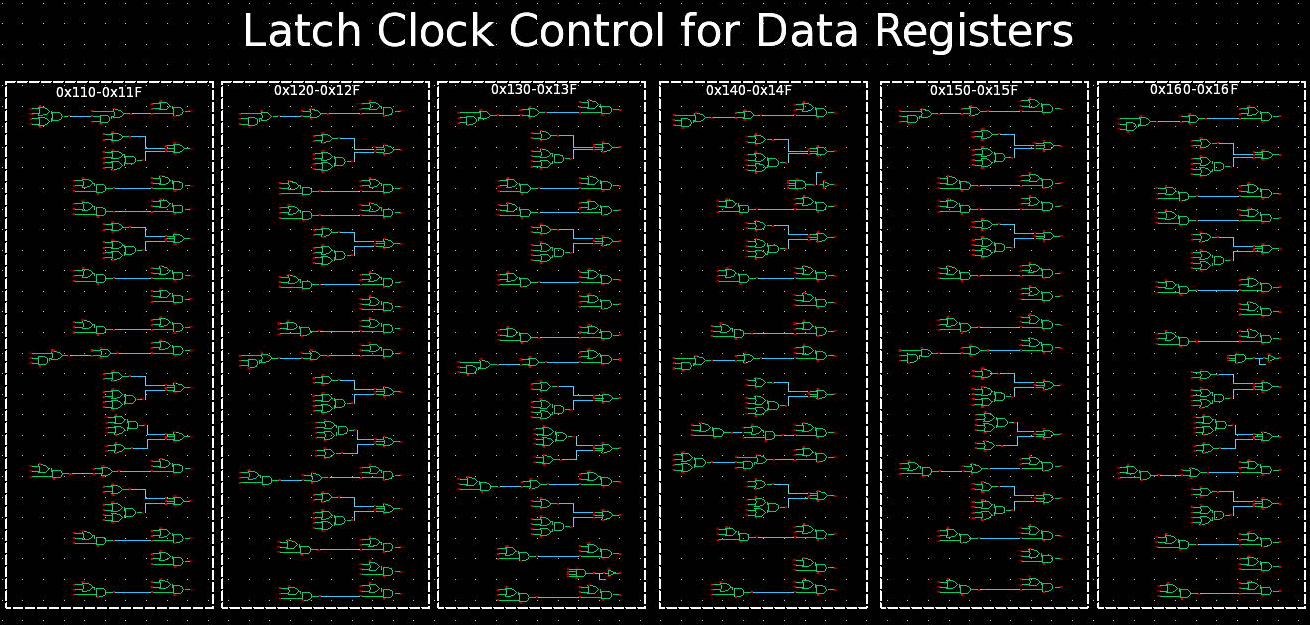

1.2. 新增数字电路中组合逻辑的BOOL仿真功能

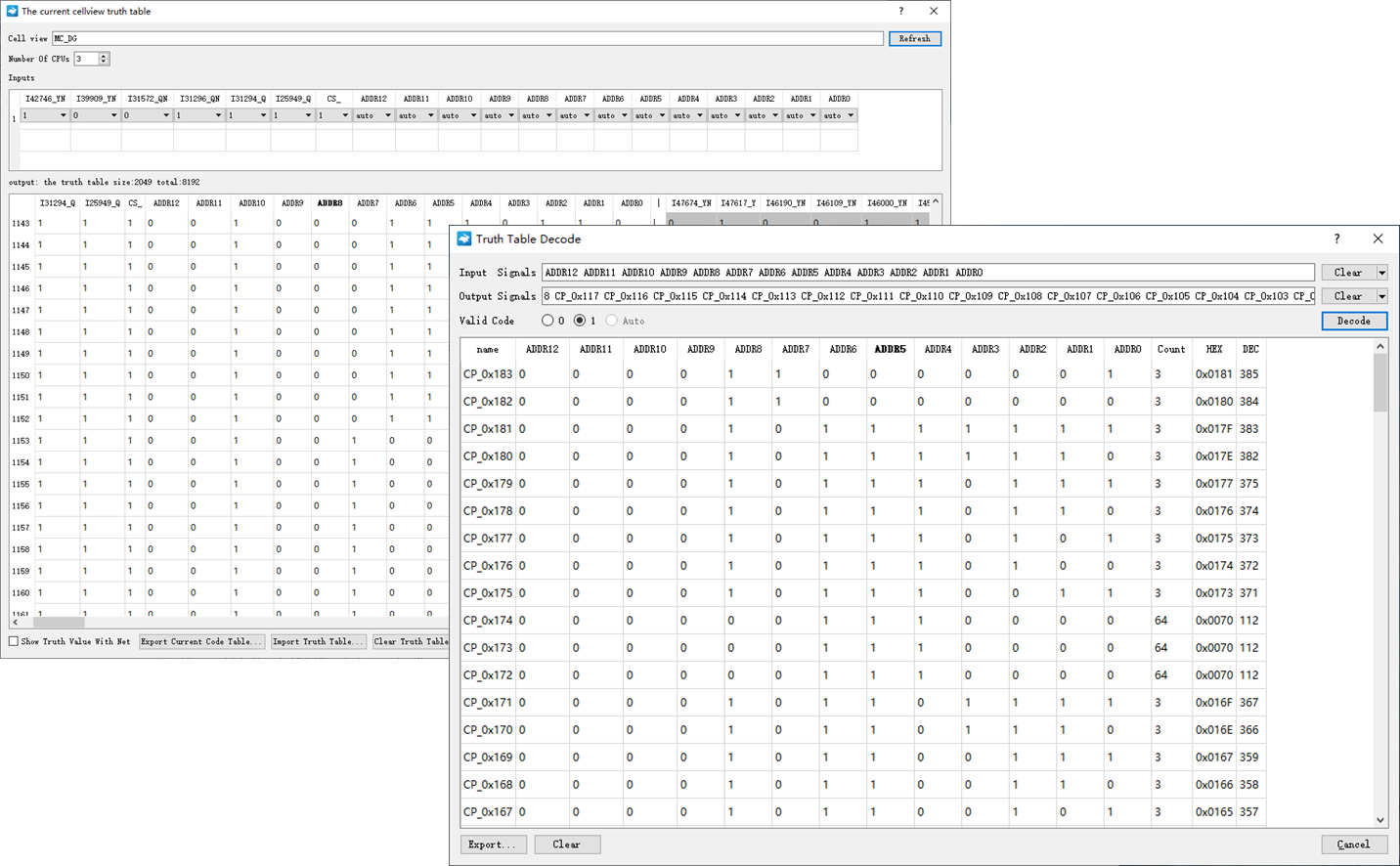

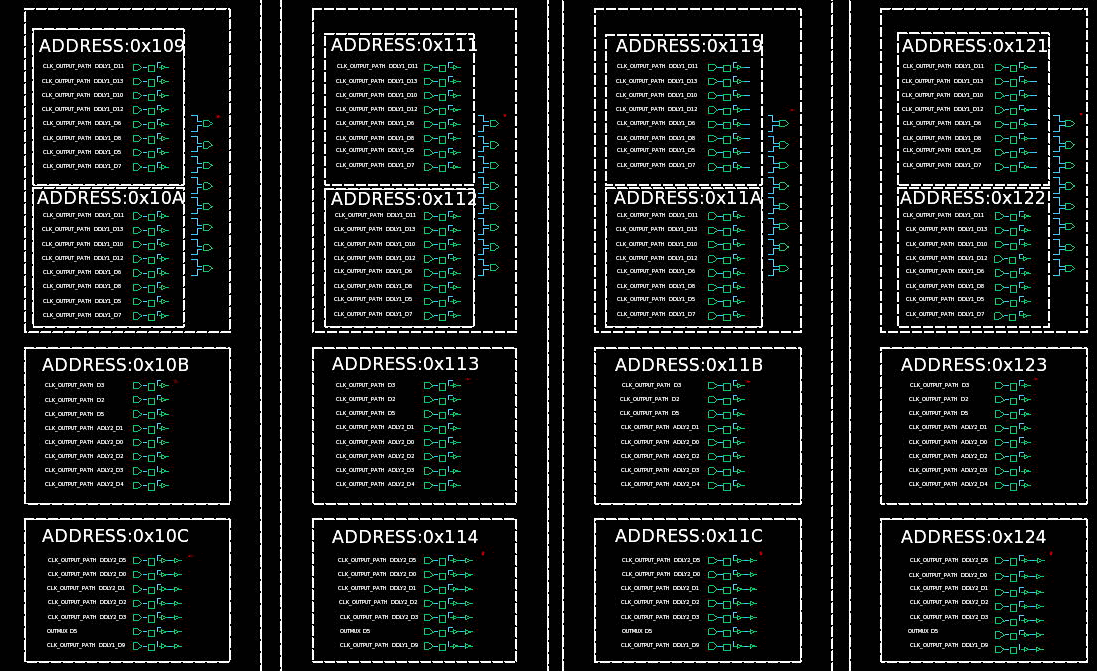

BunnyGS®软件新增了数字电路中组合逻辑的BOOL仿真功能,目前最大支持13位数据输入,即可一次完成8192次遍历运算。同时,软件支持对运算结果进行在线解码,用户可根据需要对输入输出信号进行排序和选择,在选择有效值后可直接得到解码结果。

该功能常用于分析内部线网关系复杂、实例数量较大的电路模块,如译码(器)电路、算法实现电路等,在使用时可忽略其内部复杂的结构,一次完成从输入到输出的逻辑映射,高效地完成电路分析。例如在分析以太网通讯芯片、距离传感器芯片等具有复杂寄存器映射的芯片时,使用该功能通过一次仿真即帮助工程师得到芯片的完整寄存器映射,数据流向分析因此更快更准。

1.3. 全新EDIF格式输出算法,有效取代人工替换PDK单元

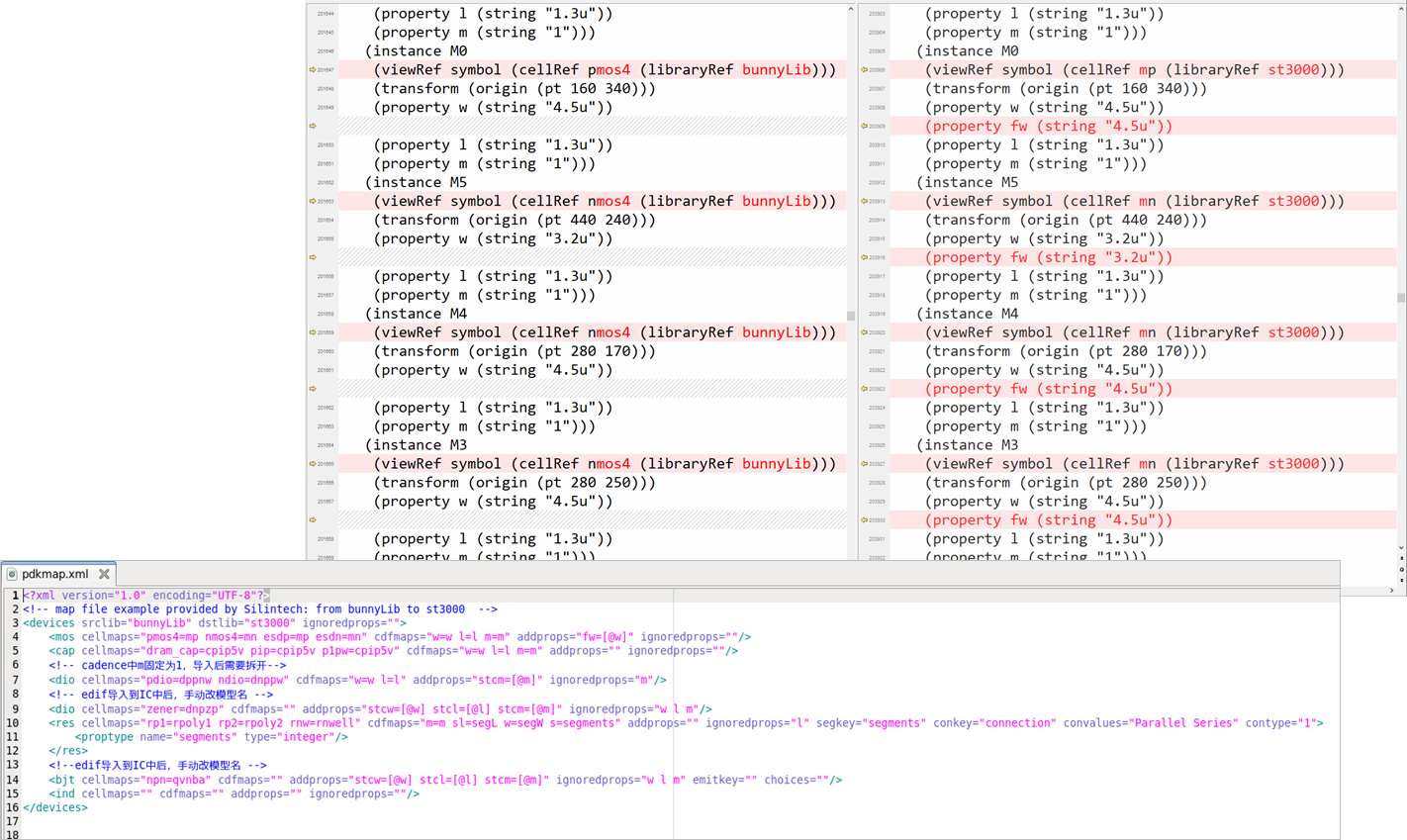

工程师设计好的电路有时需替换工艺库,不同工艺库之间的器件种类、数量及参数名称和约束等都不相同,传统的替换工艺库的方法是在视图上逐一修改器件类型。项目的器件数量巨大,逐个修改必然会带来难以估计的工作量,同时器件参数存在映射或约束关系,无法直接修改。

芯联成开发了一种高PDK兼容度的EDIF格式输出算法,通过器件库和PDK库的器件名称和参数映射关系配置pdkmap.xml文件,在导出EDIF时,软件自动将BunnyGS®提取的器件转换为相应的PDK器件,同时更新器件的参数。使用高PDK兼容度的EDIF格式输出算法后,工程师能通过导出的EDIF文件准确、高效地替换PDK库,为高效、高质量地交付项目提供了有力支撑。

pdkmap.xml文件示例

1.4. BunnyGS®系统与仿真验证软件无缝对接

大规模数字电路仿真验证中,需要导出模块的verilog文件。BunnyGS®软件支持分类别导出verilog,可以将所有基本单元的functional视图导入到同一文件中,宏模块导入到一个文件中。也可以将所有基本单元的functional视图导入到同一文件中,不同宏模块导入到不同文件中。将这些verilog文件导入到数字仿真软件进行仿真验证。

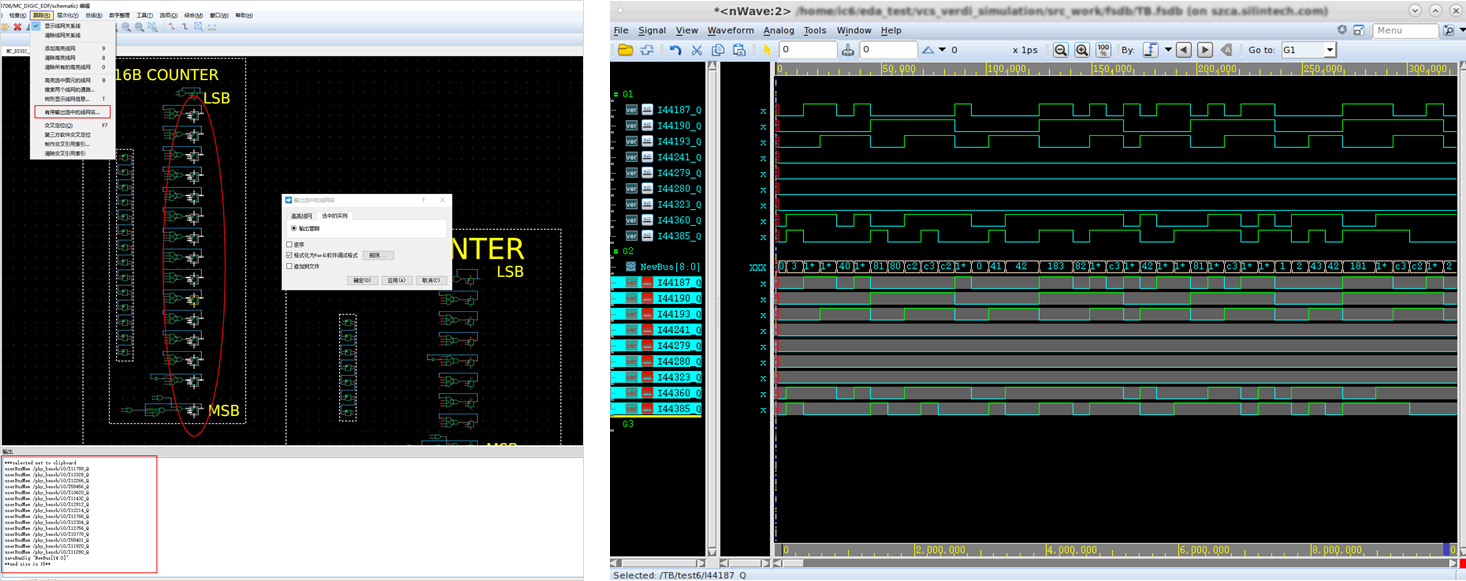

常用的数字仿真软件有Synopsys公司的VCS和Verdi、Cadence公司的 ncverilog、Mentor公司的modelsim。Verdi等软件的界面显示的实例是无序的,没有使用到规则的实例位置和有序的线网关系。

在进行验证时,通常需要使用有序的信号或能快速地找到对应的信号。BunnyGS®软件新增了格式化输出线网名功能,对于整理好的电路,可以将有序的信号格式化为Verdi软件调试格式输出,减少了复杂和繁琐的工作,方便工程师调试和跟踪信号,让工程师的工作重心落到验证上。