1. 芯片介绍

1.1 芯片概述

A5941是一款针对于中功率风扇应用的无传感器三相电机驱动芯片。这款芯片集成了正弦波信号输出驱动,因此可以最大限度得减小风扇的运行噪声和振动。在启动时,一个正弦波形的电压信号被输出到电机线圈上,平缓地启动并逐渐加速电机至所需的速度,从而实现了所谓的软启动,默认的输出电压可驱动电机工作在一个宽泛的特性范围内。另外,A5941芯片还集成有EEPROM存储单元(详见下一期介绍),根据应用需要,可以通过更改在EEPROM内存储的配置指令,定制电机的启动。电机的转速调节是通过控制PWM输入信号的占空比来实现,该PWM信号的允许频率范围非常宽。根据需求,配置EEPROM也可以设定通过模拟电压输入来调节电机转速。 A5941芯片可以实现在无需外部霍尔传感器的情况下,检测三相电机转子位置。这种技术的优点不仅可以省去因霍尔传感器的损坏而带来的维护问题,提高风扇电机的可靠性,扩大应用范围,降低生产成本,而且也能消除因传感器的不一致而产生的检测误差。A5941芯片采用了10引脚的SOIC封装形式。

A5941是一款得到广泛应用的电路芯片,在国内市场出货量比较大,但目前尚未看到相关的逆向分析介绍。

1.2 芯片特征功能

- 软启动

- 180度正弦信号输出驱动以降低运行噪声

- 高效率控制算法

- 无传感器位置检测

- 宽电源电压范围

- 速度信号输出

- 电机卡死检测

- 过电流保护

- 短路保护

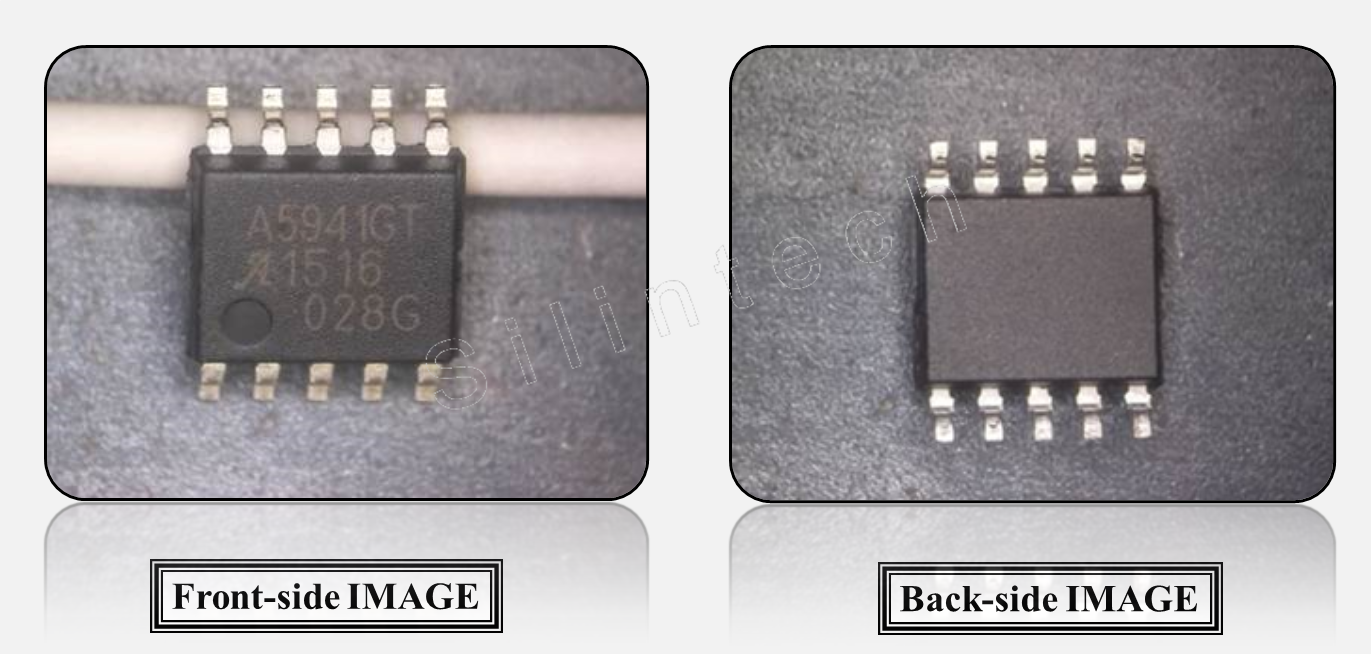

1.3 芯片封装与标记

1.3.1 芯片封装

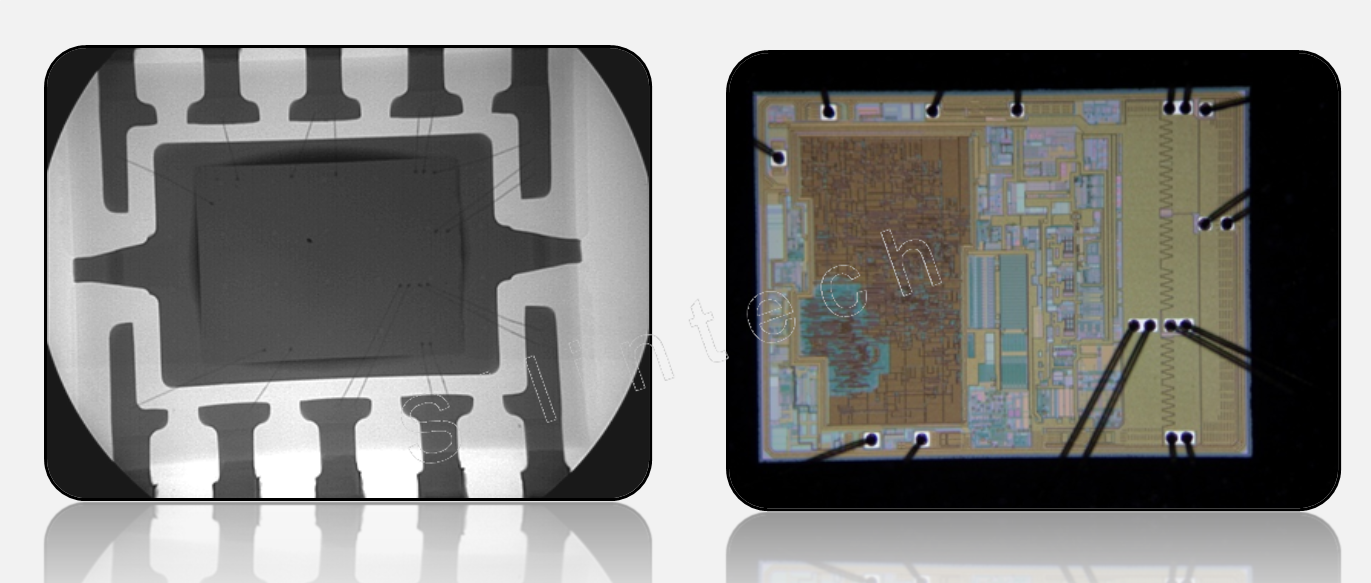

1.3.2 芯片引脚键压X光照片

1.3.3 芯片LOGO

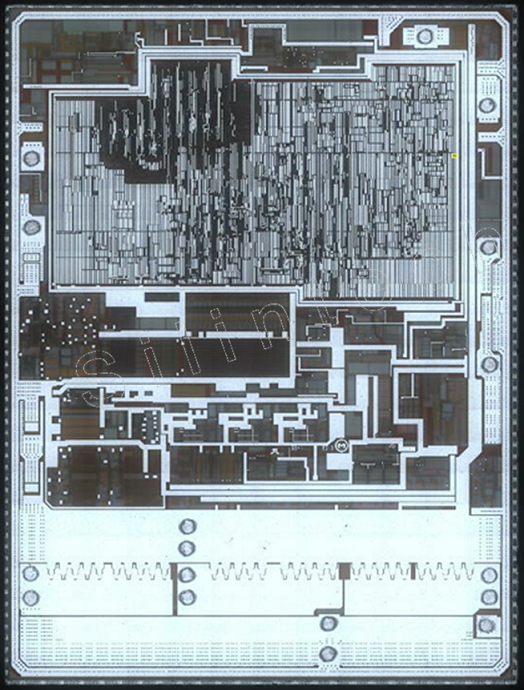

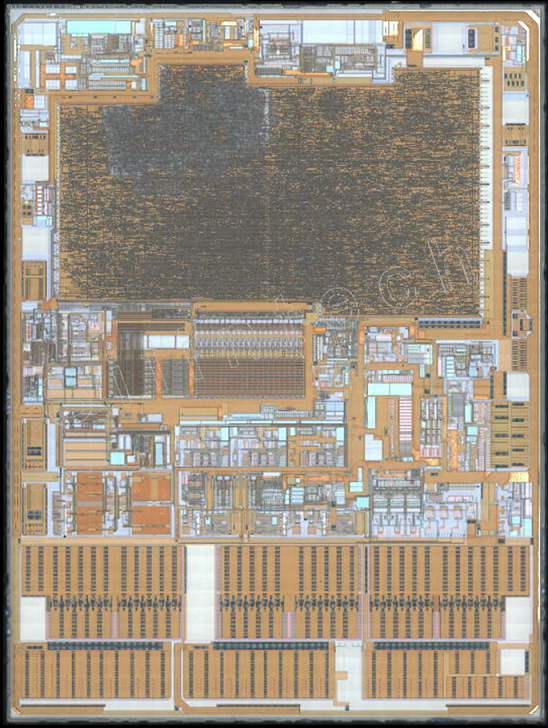

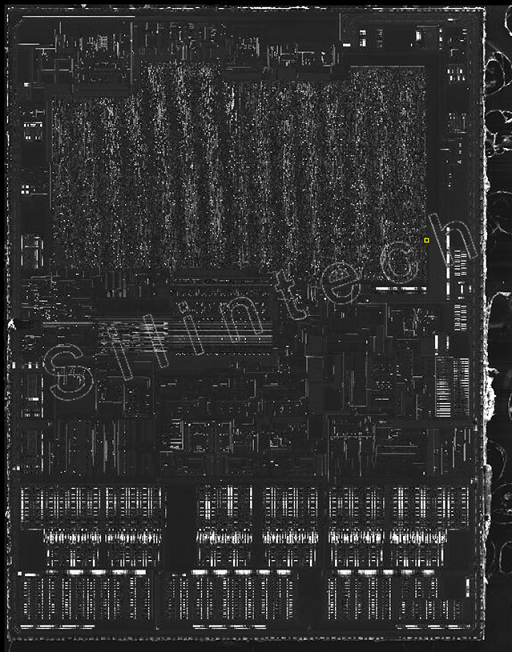

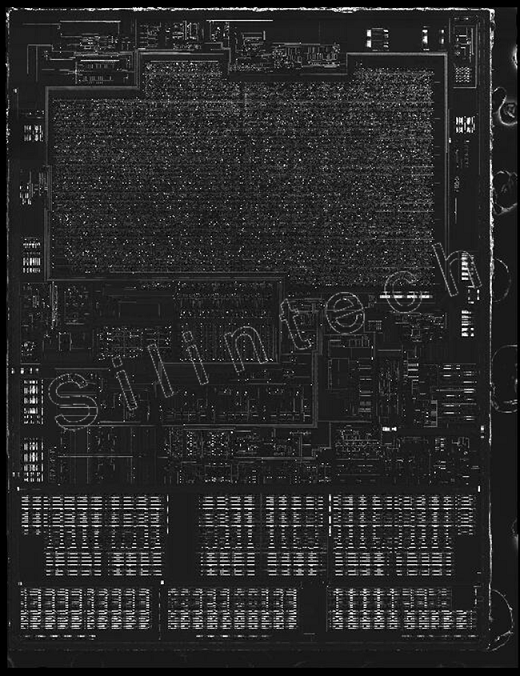

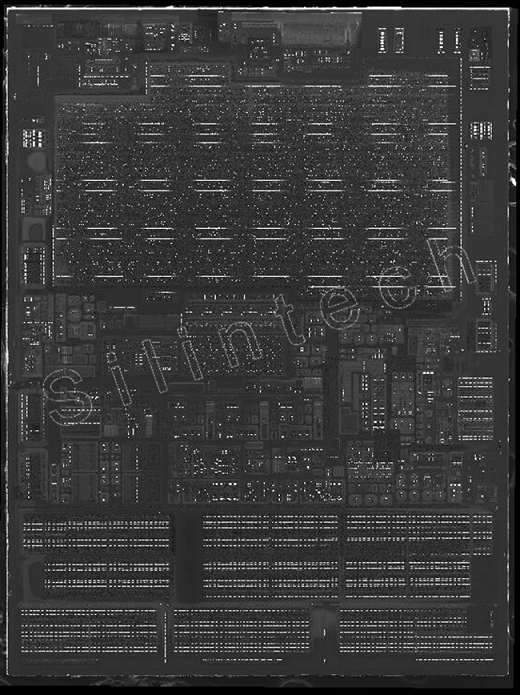

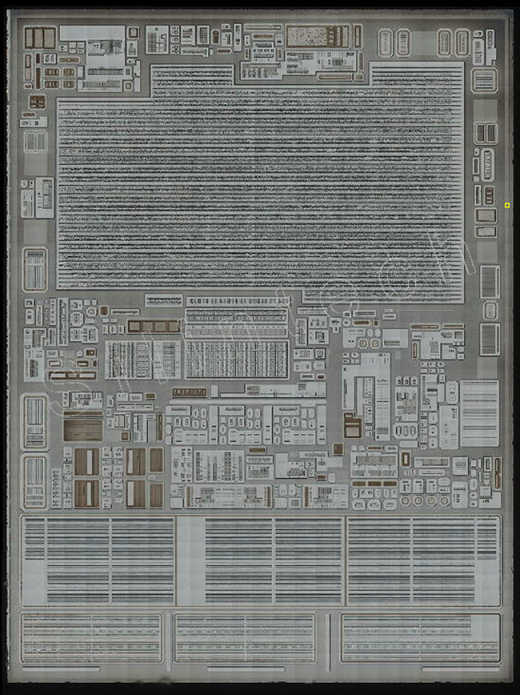

2. 芯片去层照片

2.1 Top Metal

2.2 Metal3

2.3 Metal2

2.4 Metal1

2.5 Poly

2.6 Diff

2.7 Stain

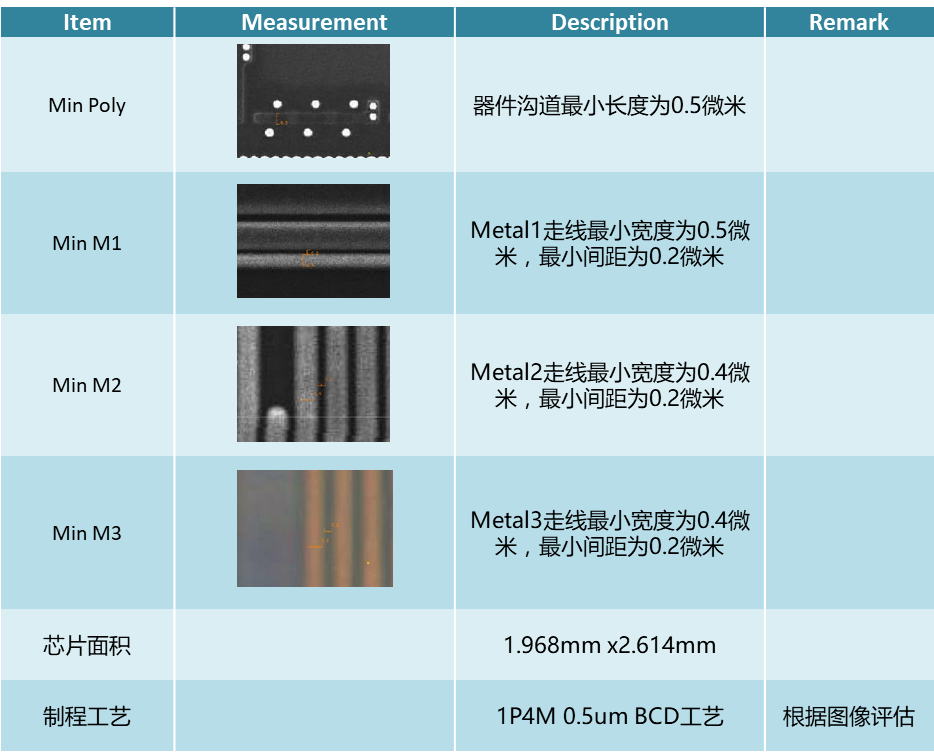

3. 芯片工艺与特征

3.1 芯片工艺评估

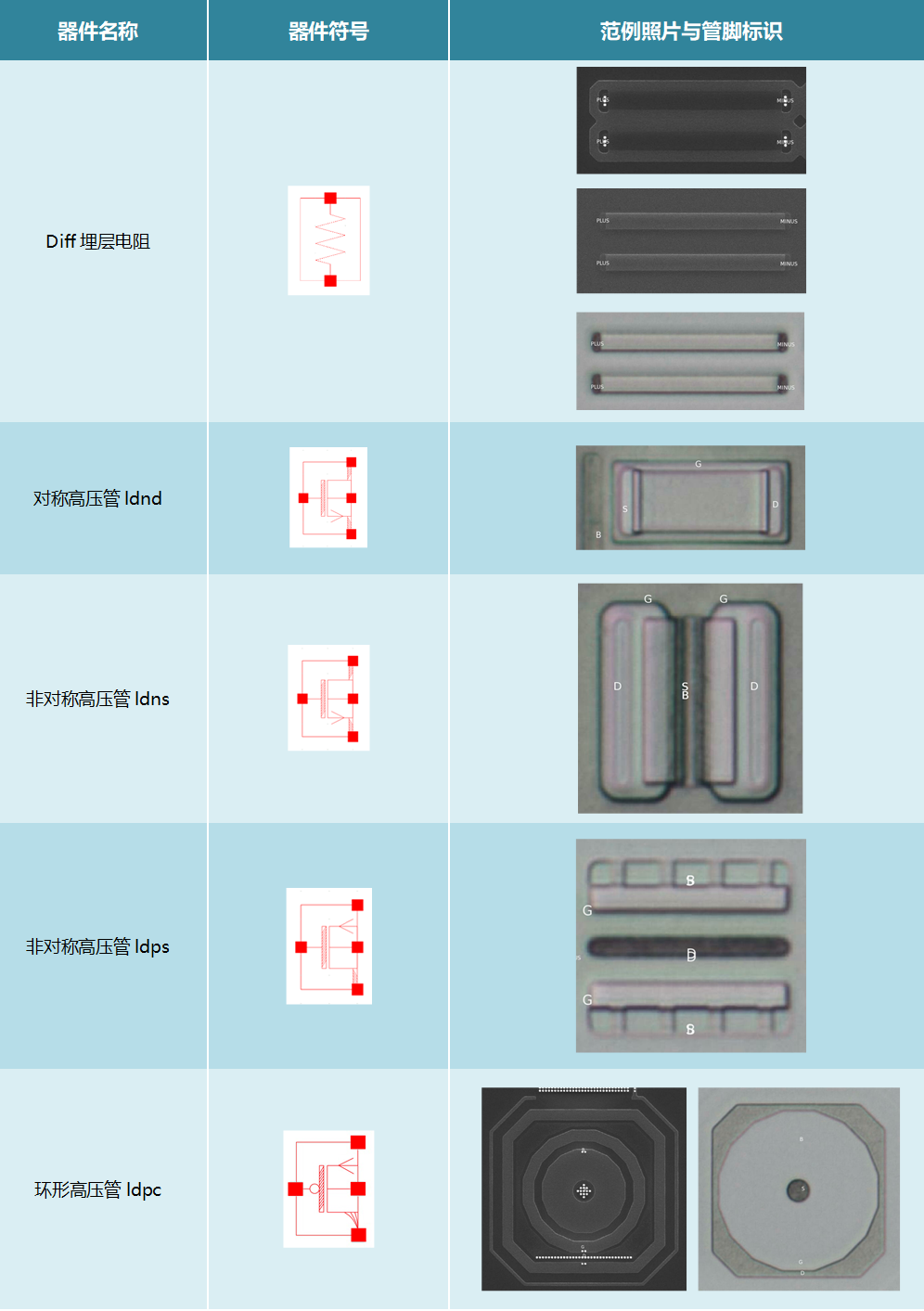

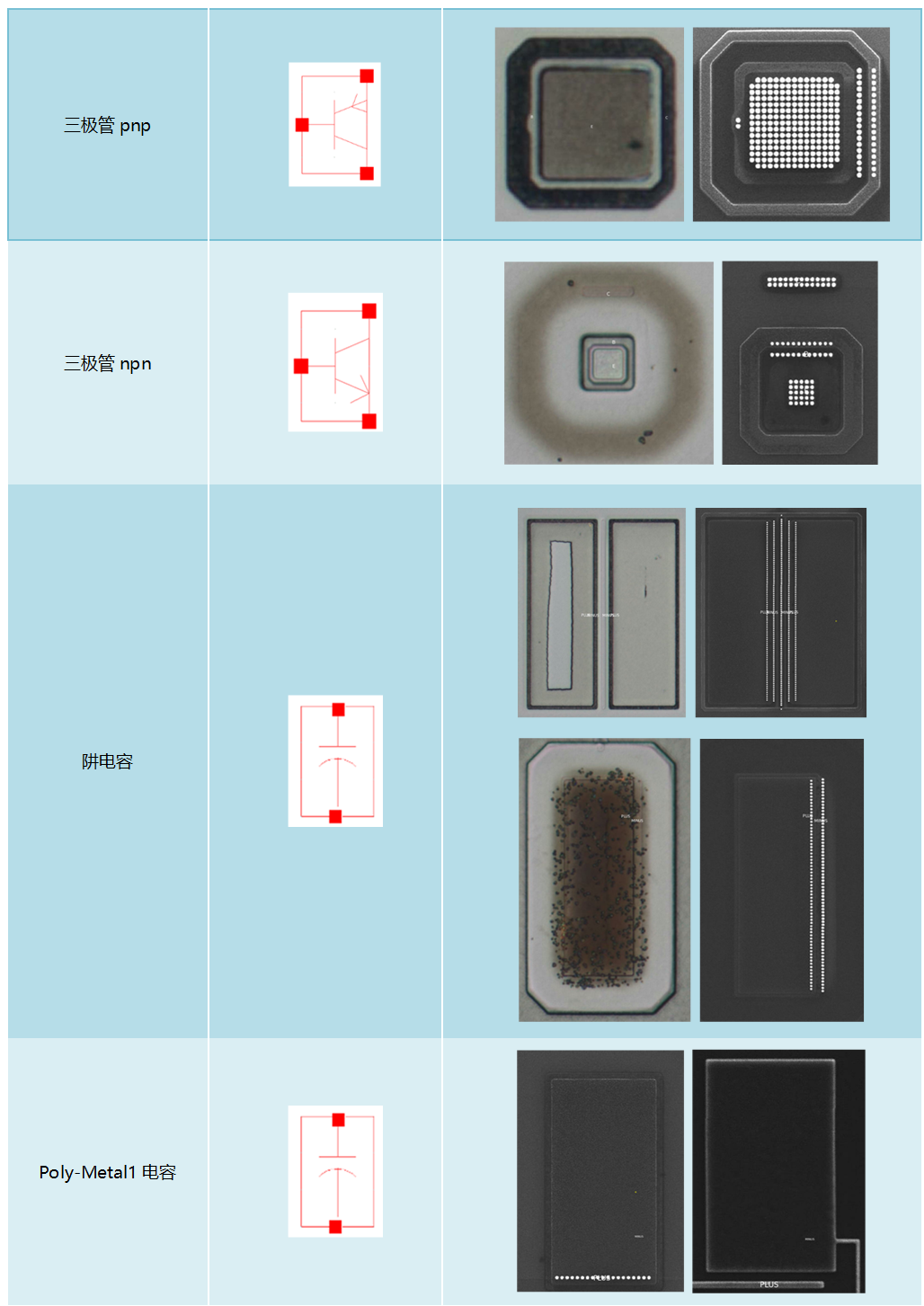

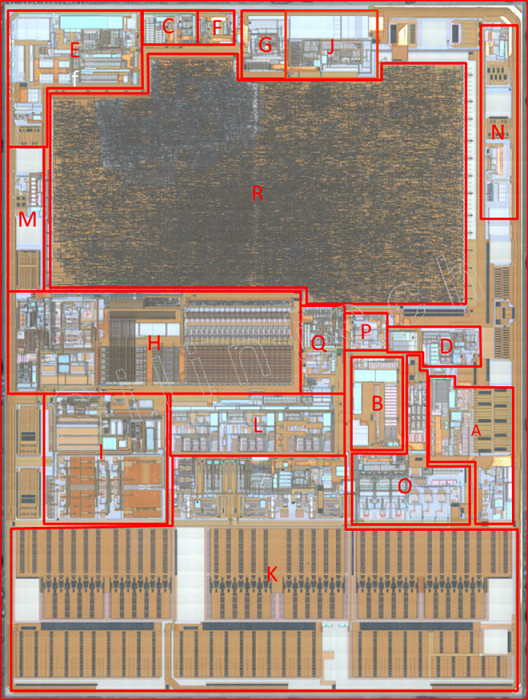

3.2 特征器件列表(不包括普通NMOS和PMOS)

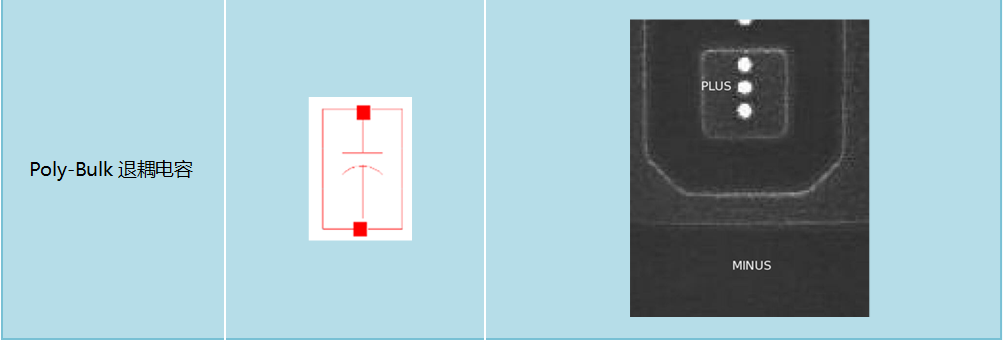

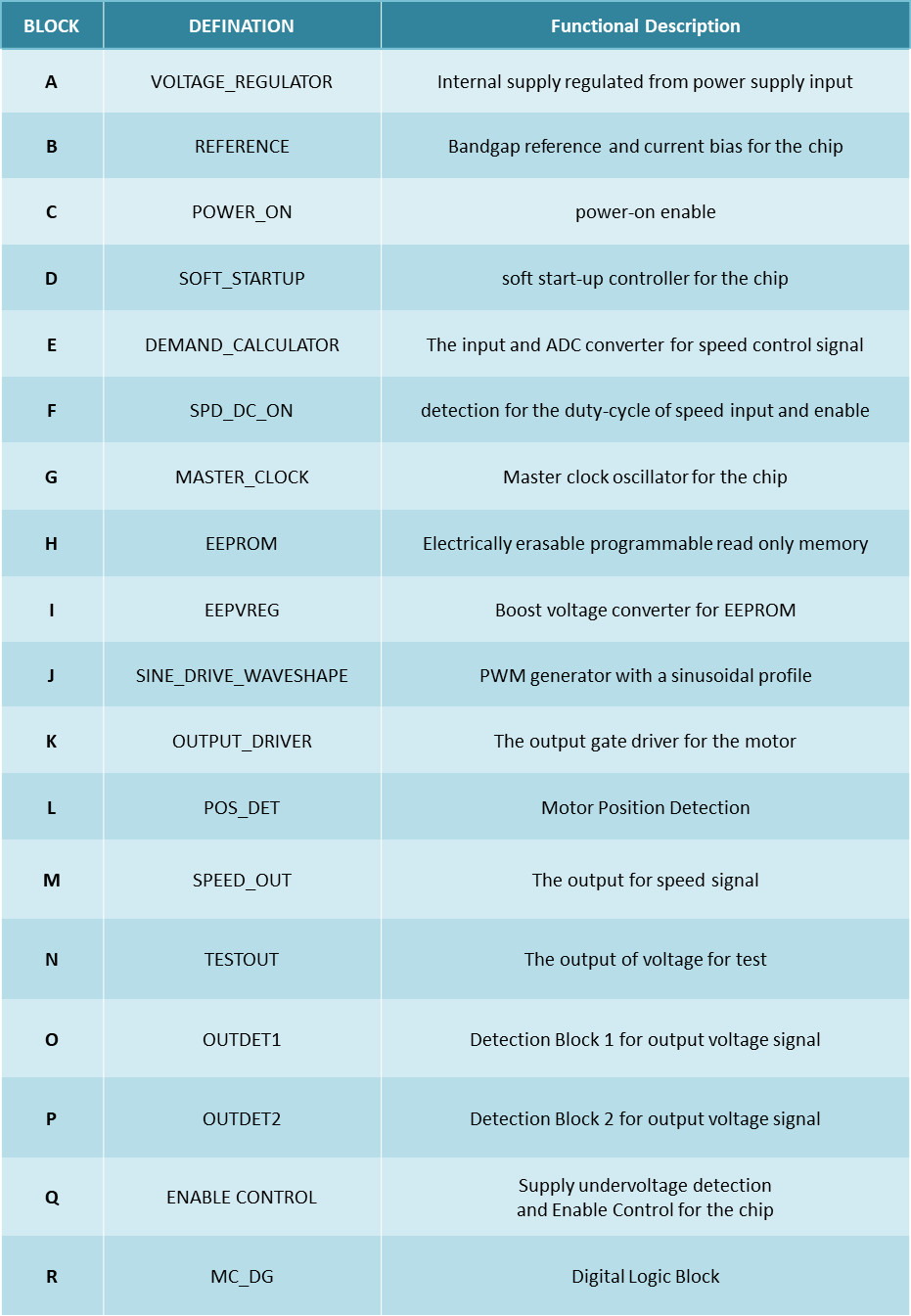

4. 芯片版图架构与功能模块划分

5.芯片电路系统架构与主要子模块原理图

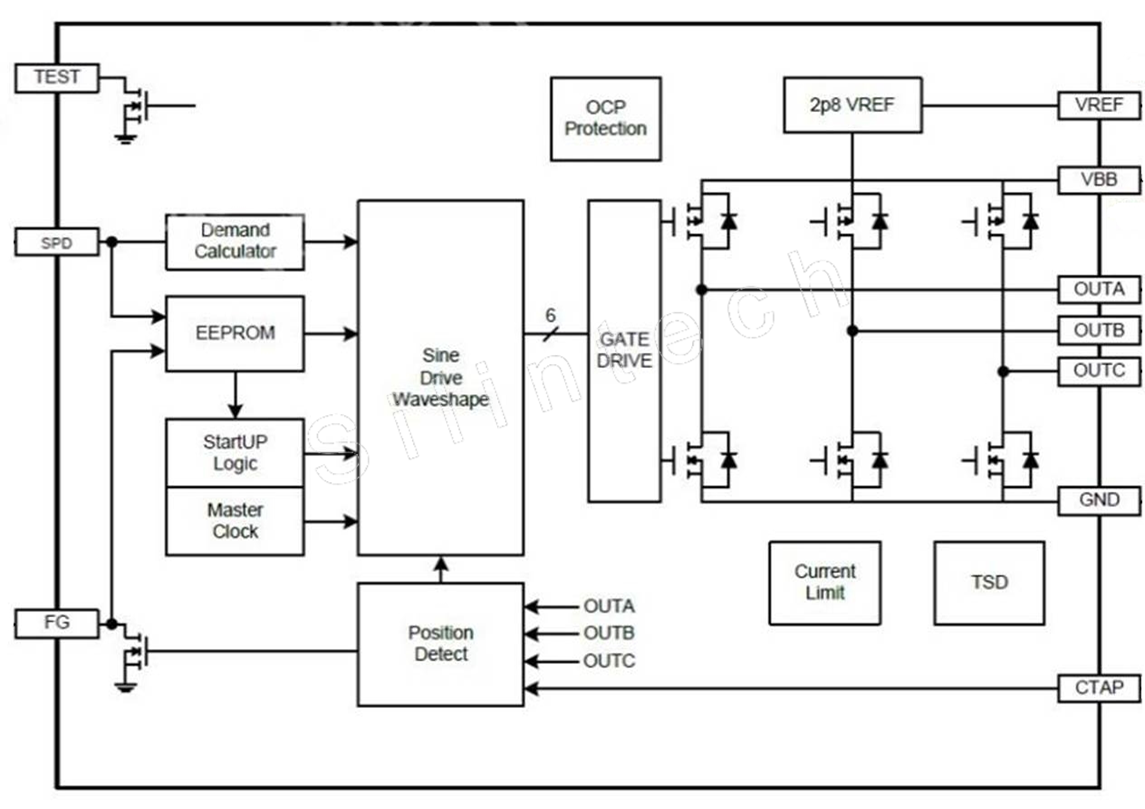

5.1 芯片datasheet系统模块图

5.2 芯联成提取整理获得的顶层电路原理图

▼Top Schematic

5.3 主要子模块电路原理图

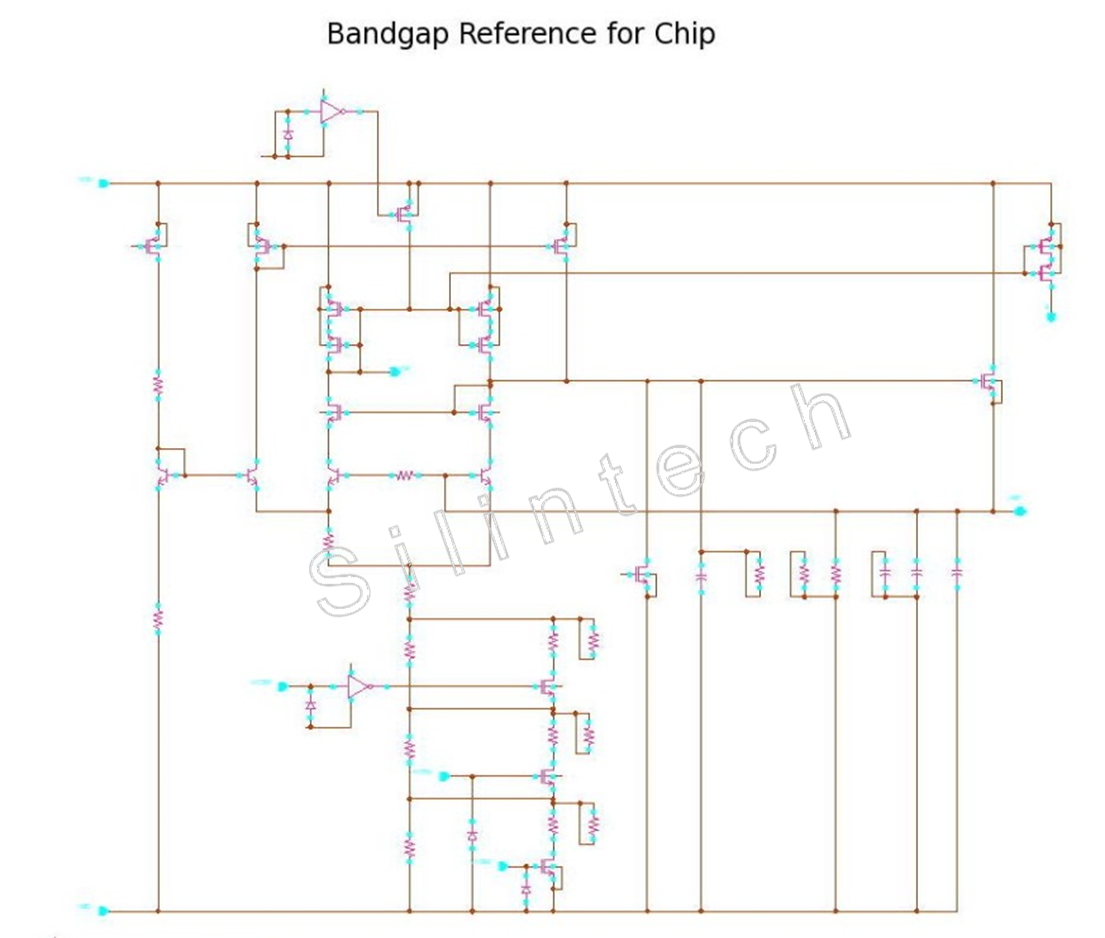

5.3.1 Bandgap基准电路

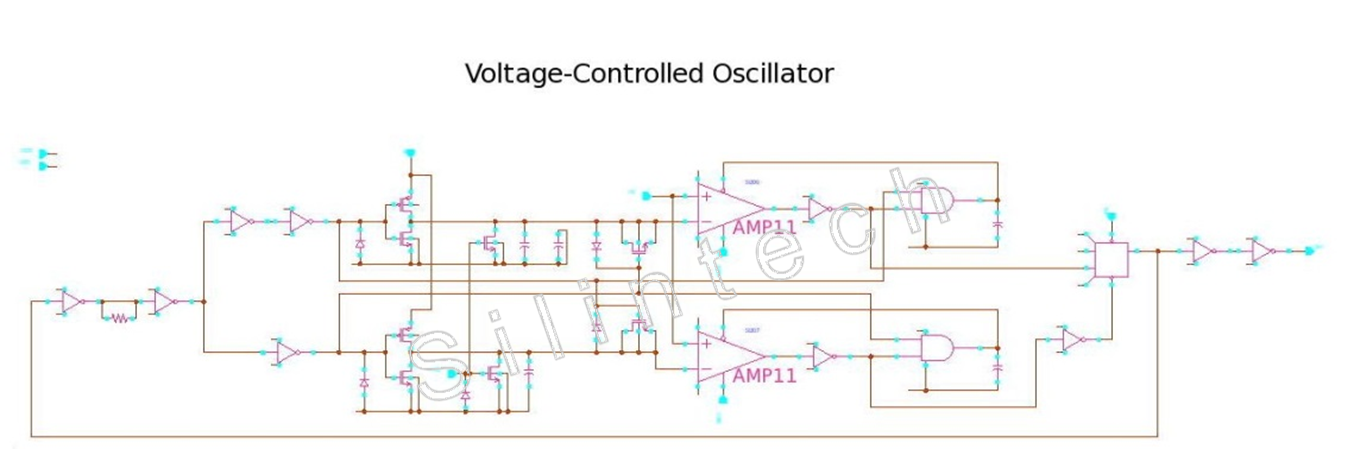

5.3.2 主时钟振荡器

5.3.3 转速控制信号输入与测量模块

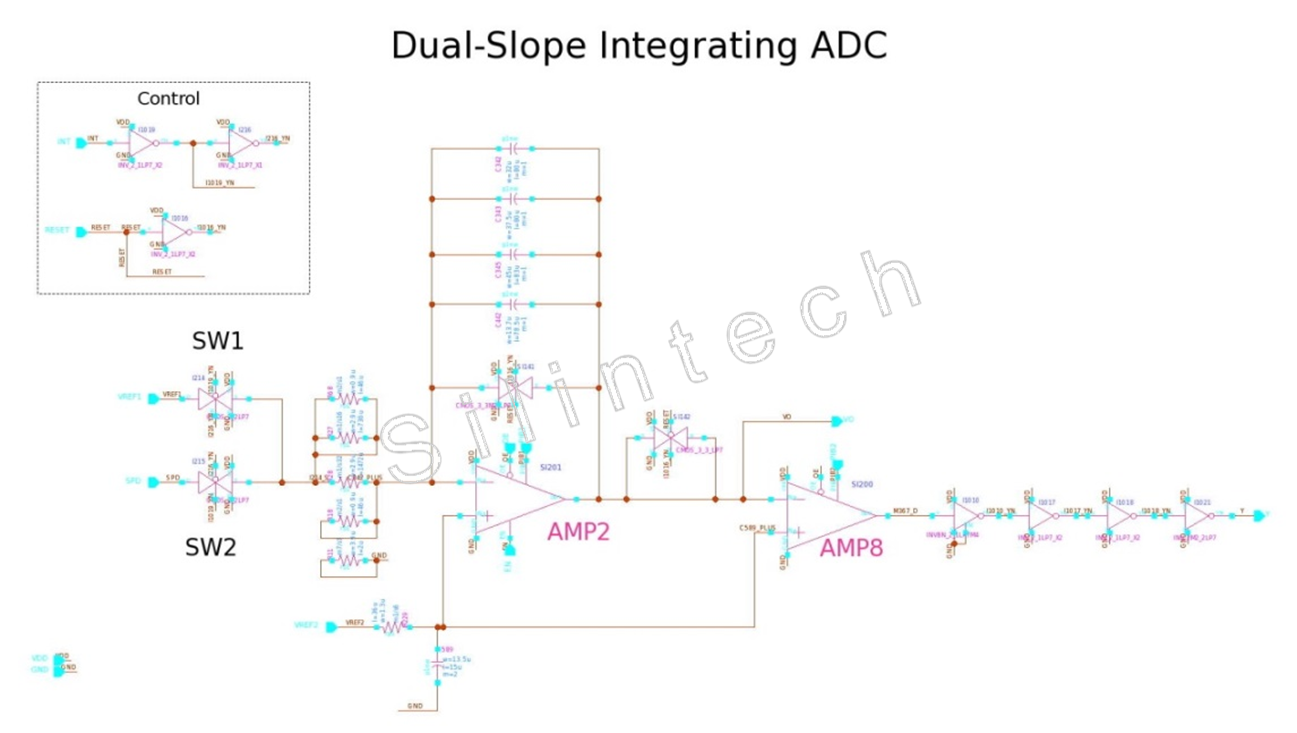

转速控制信号可以选择采用一定占空比的PWM信号输入,占空比对应转速;也可以采用模拟电压信号输入,电压对应转速。模拟输入电压信号通过模数转换电路(ADC)被转换成9位数字值。ADC采用双斜率积分算法,电路原理图如图所示,其中运放AMP2对电容进行充放电积分运算,运放AMP8起比较器作用。首先,开关SW1关闭,SW2打开,参考电压对积分电容进行充电,充电时间固定,然后SW1关闭,SW2打开,输入转速控制电压对积分电容进行放电回到初始电平,因此放电时间与充电时间之比值能够直接反映输入电压与参考电压之比,通过一个高精度计数器可以很方便的直接获得输入电压的数字转换值。运放AMP8为两级运放,高增益减小比较误差。

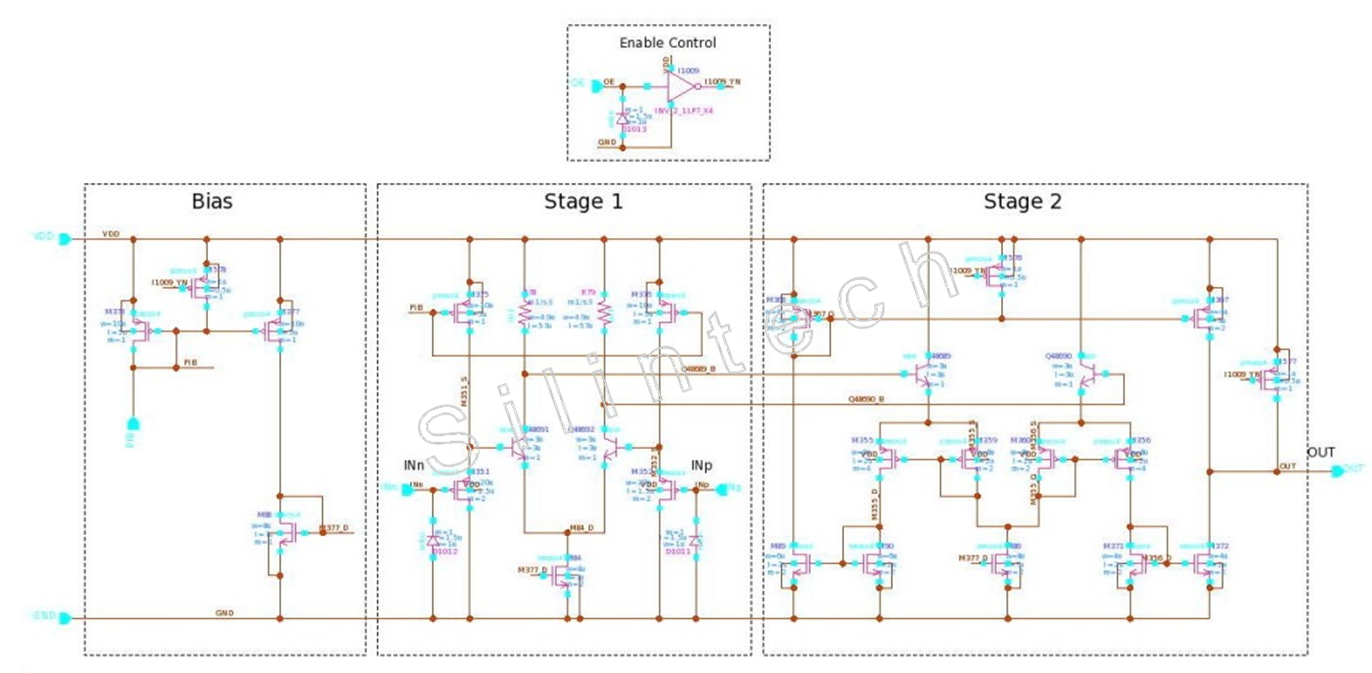

▼AMP8

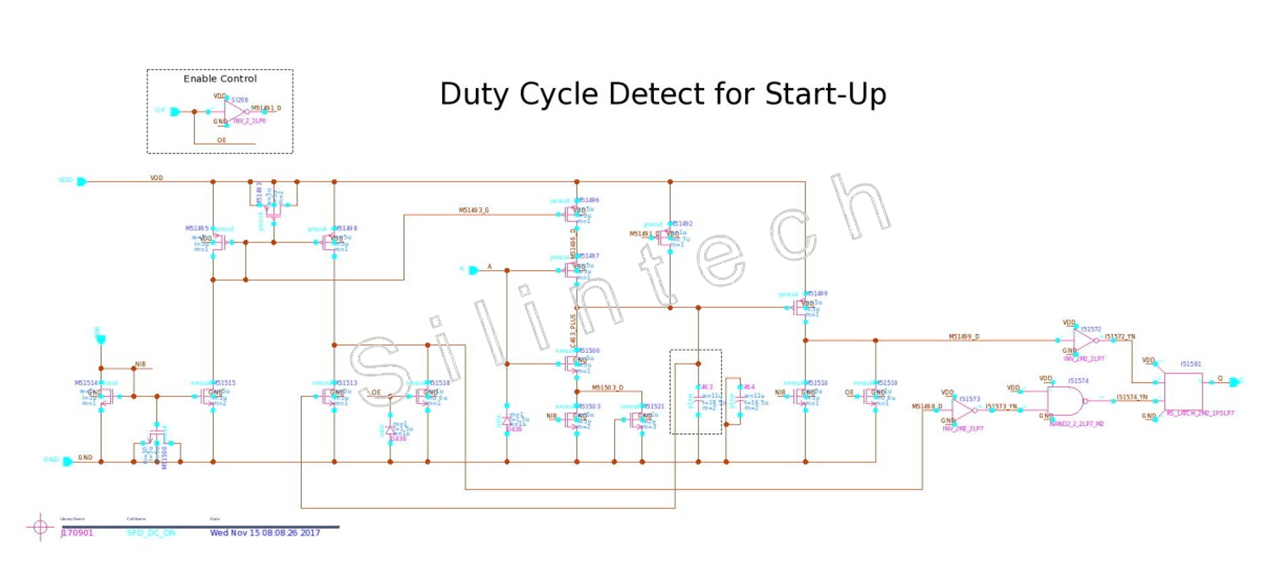

5.2.4 PWM输入占空比监测启动电路

本电路检测输入转速控制PWM信号的占空比是否达到芯片工作启动条件,当输入为模拟电压信号,该信号也会转换为一定占空比的PWM信号,占空比对应电压幅值,并通过本电路检测是否触发芯片工作启动条件。当占空比不足时,虚线内积分电容无法充到足够电压以开启相连的NMOS管,从而无法产生启动信号,让芯片工作。

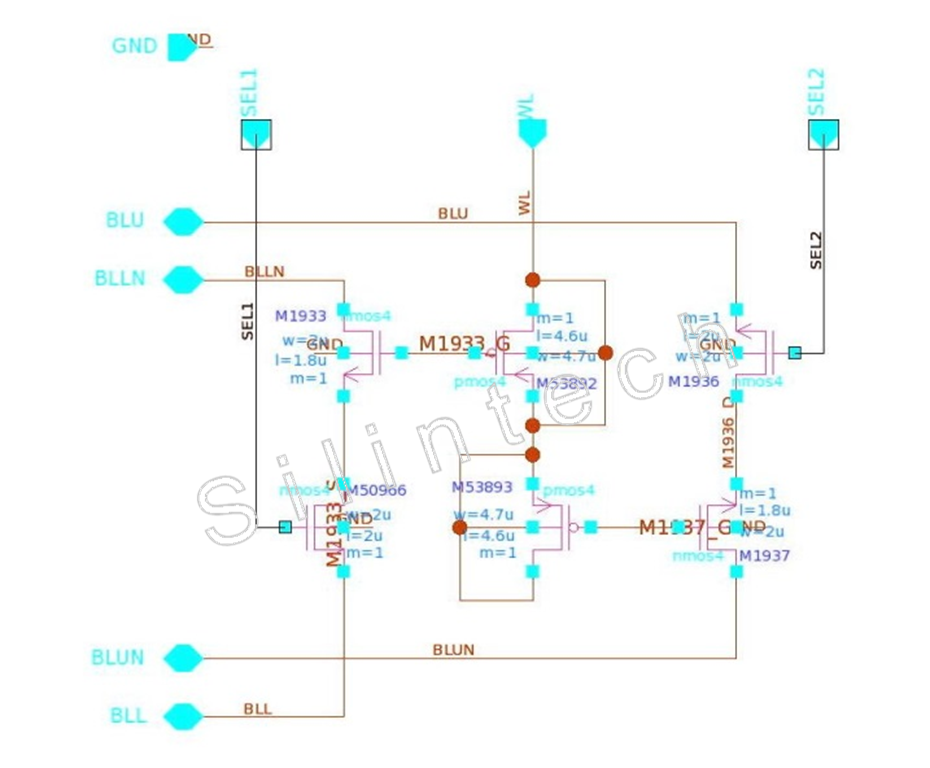

5.2.5 EEPROM存储基本单元

A5941集成了一个24X20阵列,共480bit的EEPROM存储单元,单元结构如下,由两个bit并联组成。图中一个PMOS和一个NMOS共用一个栅极连接,该栅极为浮栅,用于存储电荷,记忆写入"0"或“1"状态,串联的NMOS做单元选择开关管。

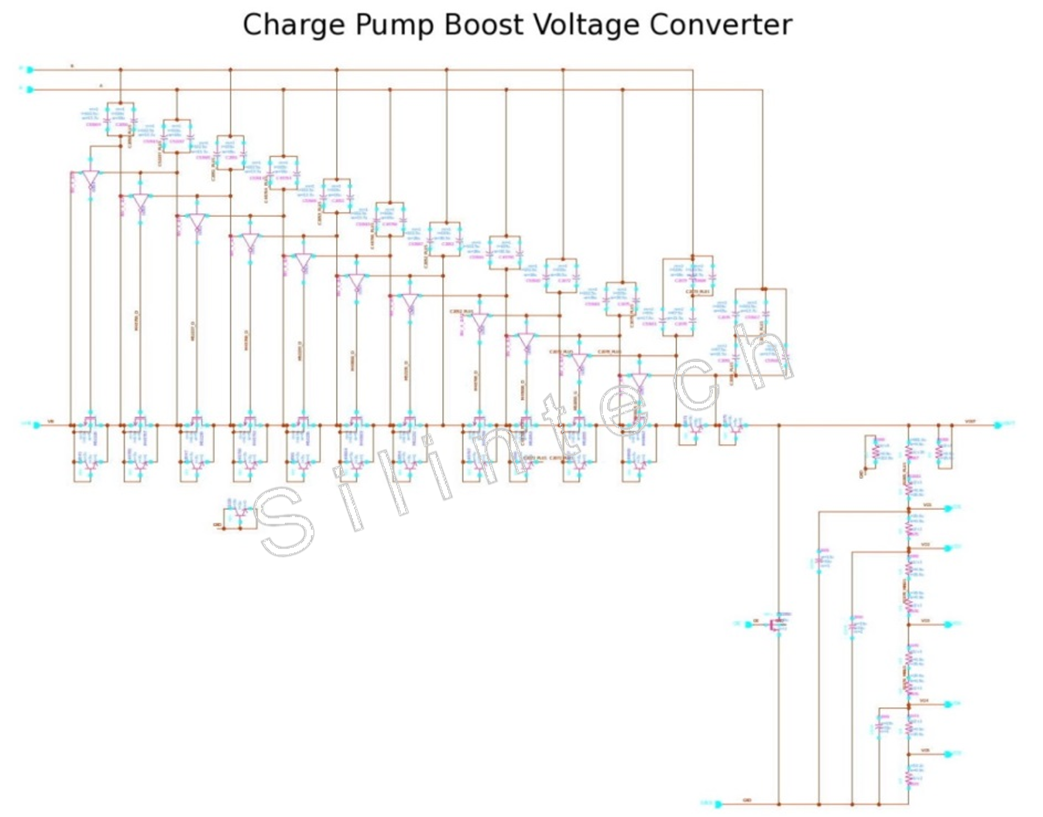

5.2.6 电荷泵DC-DC升压变换器

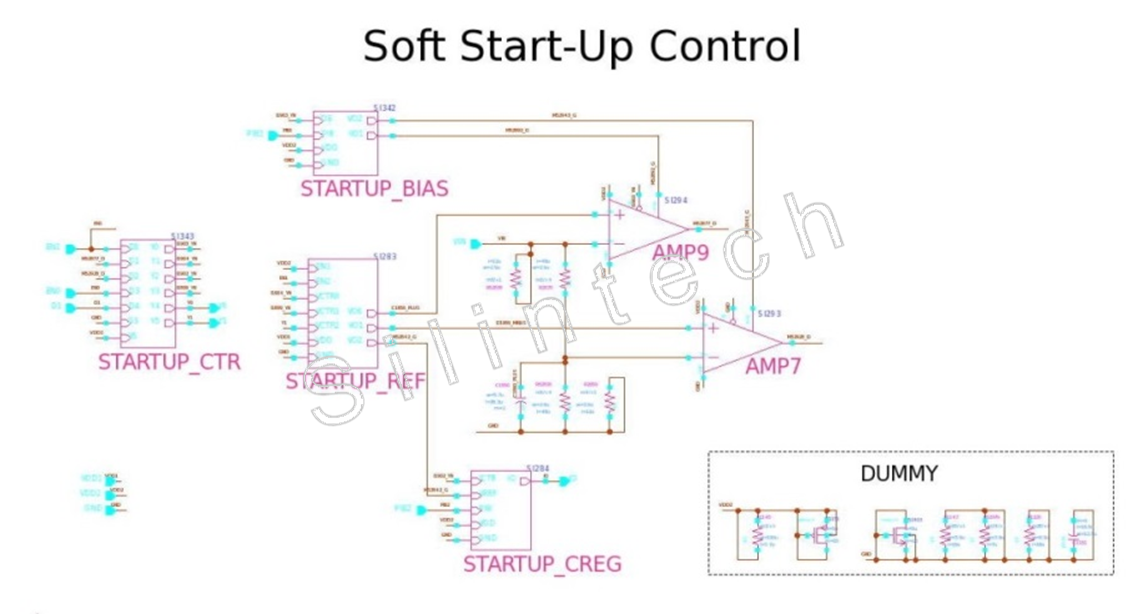

5.2.7 软启动控制

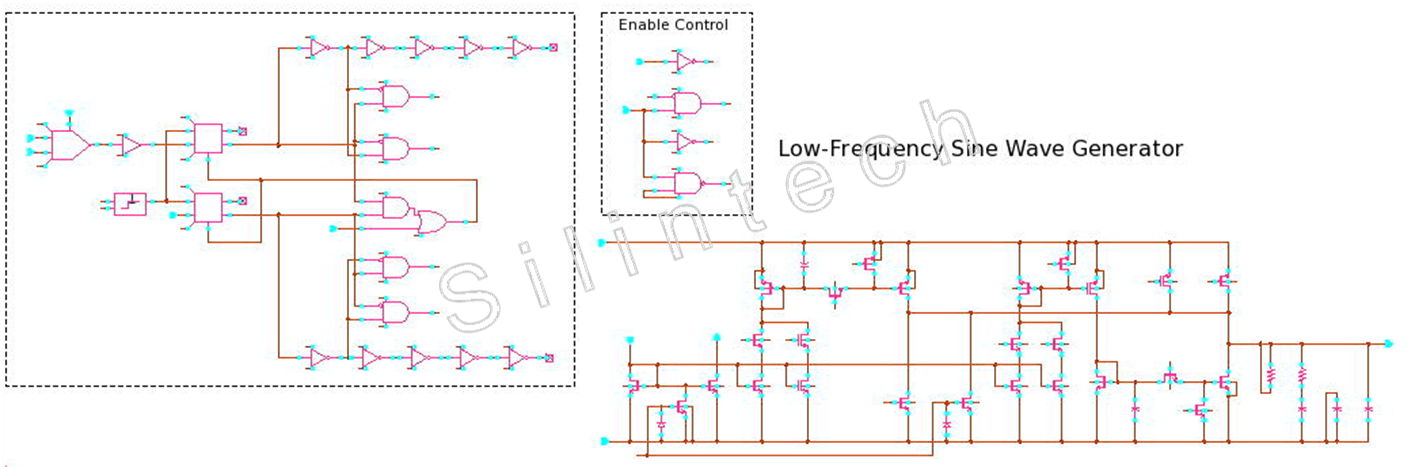

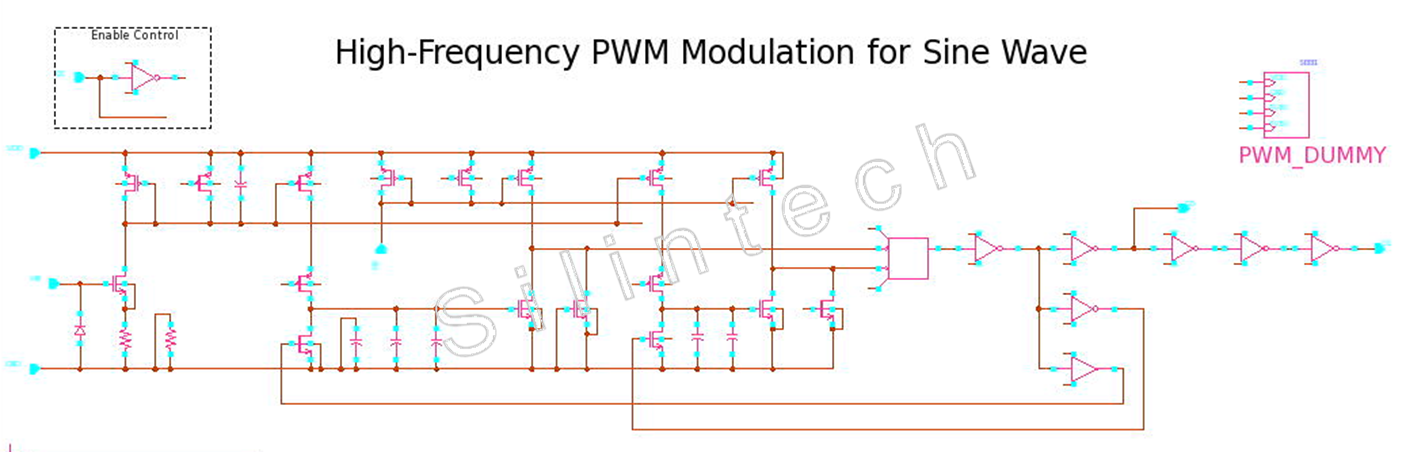

5.2.8 正弦波PWM生成模块

▼SINEWAVE_GEN Block

▼SINEWAVE_MOD Block

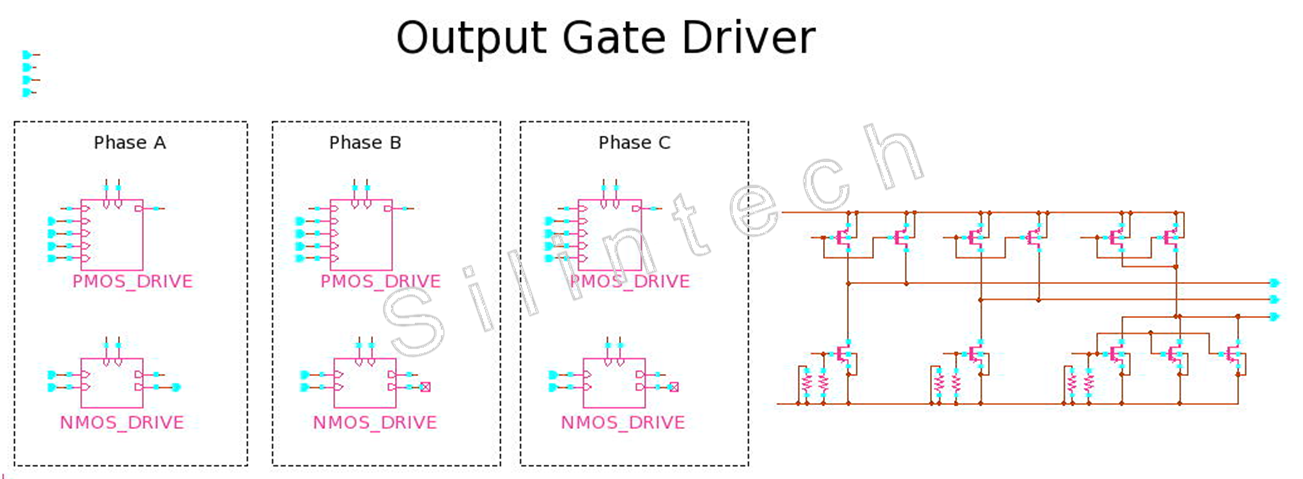

5.2.9 输出驱动

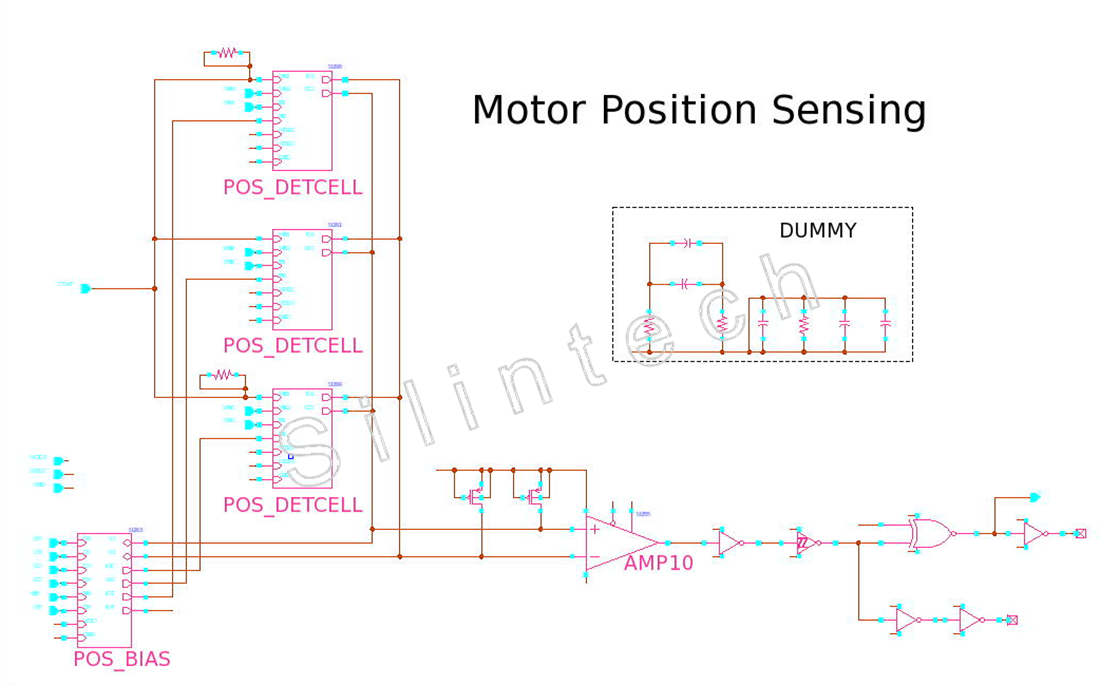

5.2.10 位置检测电路

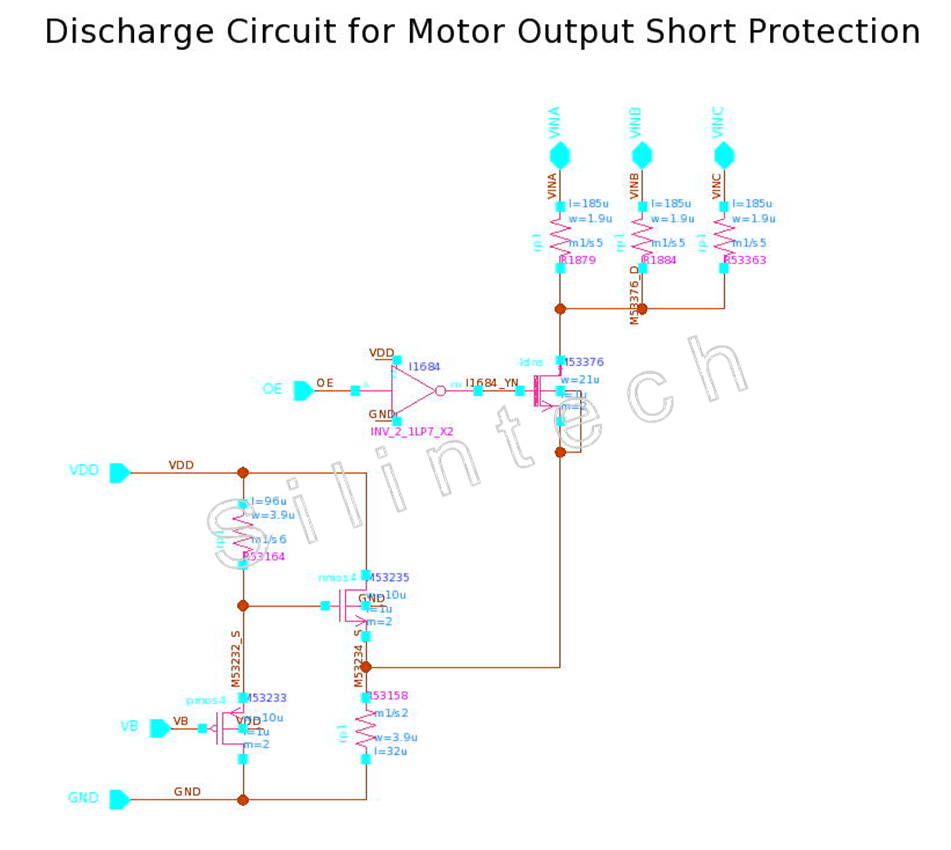

5.2.11 输出短路保护电路

对于三相电机驱动输出,当三相输出正常时,采用星型连接的负载的中心点为最低电平,接近与地,此时本电路不导通;当某一相输出短路时,中心点电位急剧上升,本电路导通提供大电流泄放通道,由此保护三相电机绕组线圈不被烧坏。

6. 芯联成层次化电路原理图结构列表

5.1 Voltage Regulator

5.1.1 VREG1

5.1.1.1 VREG_BIAS

5.1.1.2 AMP6

5.1.2 VREG2

5.2 Reference and Bias

5.2.1 BANDGAP

5.2.2 PRIBIAS

5.2.3 SECBIAS

5.3 MASTER_CLOCK

5.3.1 MC_VCO

5.3.1.1 AMP11

5.3.2 MC_BIAS

5.3.3 MC_ENABLE

5.3.4 MC_DELAY

5.4 Soft Start-Up and Enable Control

5.4.1 POWER_ON

5.4.2 SOFT_STARTUP

5.4.2.1 AMP9

5.4.2.2 AMP7

5.4.2.3 STARTUP_BIAS

5.4.2.4 STARTUP_REF

5.4.2.5 STARTUP_CTR

5.4.2.6 STARTUP_CREG

5.4.2.6.1 AMP5

5.4.3 CTR_ENABLE

5.5 SPD Demand Calculator

5.5.1 SPD_PWM_INPUT

5.5.1.1 SPD_PWM_CONV

5.5.1.2 SPD_PWM_LPF

5.5.2 SPD_INPUT_ADC

5.5.2.1 SPD_BIAS

5.5.2.2 SPD_VREF

5.5.2.3 ANALOG_INPUT

5.5.2.3.1 AMP4

5.5.2.4 SPD_ADC

5.5.2.4.1 AMP2

5.5.2.4.2 AMP8

5.5.2.5 TESTO2

5.5.3 SPD_DC_ON

5.5.4 CTR_SPD

5.6 SPEED_OUT

5.7 EEPROM BLOCK

5.7.1 EEPROM

5.7.1.1 REFERENCE

5.7.1.1.1 EEPROM_PG_REF

5.7.1.1.1.1 EEPROM_PWR_REF

5.7.1.1.1.2 EEPROM_GND_REF

5.7.1.1.1.3 EEPROM_VREF3

5.7.1.1.2 EEPROM_REF

5.7.1.1.2.1 EEPROM_BIAS

5.7.1.1.2.2 EEPROM_VREF1

5.7.1.1.2.2.1 AMP1

5.7.1.1.2.3 EEPROM_VREF2

5.7.1.1.2.4 EEPROM_VB_MUX

5.7.1.2 EEPROM_CELL_ARRAY

5.7.1.2.1 EEPROM_CELL

5.7.1.3 EEPROM_COLUMN_CTR

5.7.1.3.1 EEPROM_COLUMN_CTR1

5.7.1.4 EEPROM_COLSEL_DEC

5.7.1.5 EEPROM_VWL

5.7.1.5.1 EEPROM_VREF4

5.7.1.6 EEPROM_WR_CONTROL

5.7.1.6.1 EEPROM_WR_CTR_CELL

5.7.1.7 EEPROM_ROWSEL

5.7.1.8 EEPROM_DATAOUT

5.7.1.9 EEPROM_CTR_DEC

5.7.1.10 EEPROM_DUMMY

5.7.2 EEPVREG

5.7.2.1 EEPVREG_BIAS2

5.7.2.2 EEPVREG_DAC

5.7.2.2.1 AMP14

5.7.2.3 AMP15

5.7.2.4 EEPVREG_CTR

5.7.2.5 EEPVREG_DDRIVER

5.7.2.6 BOOST_CONVERTER

5.7.2.7 EEPVREG_LEVEL_DET

5.7.2.7.1 EEPVREG_BIAS1

5.7.2.7.2 AMP13

5.7.2.8 EEPVREG_AMP_CTR

5.7.2.9 TESTO3

5.8 SINE_DRIVE_WAVESHAPE

5.8.1 SINEWAVE_GEN

5.8.2 SINEWAVE_MOD

5.8.3 FREQ_DIVIDER

5.8.2.1 PWM DUMMY

5.9 OUTPUT

5.9.1 OUTPUT_BIAS

5.9.2 CTR_OUTPUT

5.9.3 OUTPUT_DRIVER

5.9.3.1 PMOS_DRIVE

5.9.3.1.1 PDRIVE_VREG

5.9.3.1.2 AMP17

5.9.3.2 NMOS_DRIVE

5.10 Motor Position Detection (POS_DET)

5.10.1 POS_BIAS

5.10.2 POS_DETCELL

5.10.2.1 POS_VREG

5.10.3 AMP10

5.11 Output Detection

5.12 TESTOUT

5.13 BIAS_EEP_TSO

5.14 Protection Circuits

5.14.1 UVLO

5.14.2 OTP

5.14.2.1 OTP_BIAS

5.14.2.2 AMP16

5.14.2.3 TESTO1

5.14.3 OSP

5.15 INTERFACE

5.15.1 INTF_BIAS

5.15.2 BUFFER

5.16 PAD ESD

5.16.1 ESD1

5.16.2 ESD2

5.16.3 ESD3

5.17 Basic Digital Cell

5.17.1 AND2B1_2M2_2LP7

5.17.2 AND2_2M2_1P8

5.17.3 AND2_2M2_2LP7

5.17.4 AND2_5_2P5_L1P5_M2

5.17.5 AND2_5_2P5_L1P5_M2_X1

5.17.6 AND_2M2_1LP7

5.17.7 AO21_2M2_2LP7

5.17.8 AOI22_2M2_1P8

5.17.9 BUFX2_2M2_2LP7

5.17.10 BUFX2_2M4_1P8M2

5.17.11 BUFX2_2M4_2LP7M2

5.17.12 BUFX2_2M8_2LP7M4

5.17.13 BUFX2_2_1LP7

5.17.14 CMOS_10_10_LP8

5.17.15 CMOS_2M2_2LP7

5.17.16 CMOS_2_2LP7

5.17.17 CMOS_2_2LP7_M2

5.17.18 CMOS_2_2_M2

5.17.19 CMOS_3_3M2_LP7

5.17.20 CMOS_3_3_LP7

5.17.21 CMOS_4_2

5.17.22 CMOS_5_2LP7

5.17.23 CMOS_5_5_LP7

5.17.24 DFFR_2M2_2LP7

5.17.25 DLATCH_2M2_2LP7

5.17.26 DLATCH_2M2_2LP7_X1

5.17.27 DLATCH_5L1P5_4L2

5.17.28 INVBN_2_1LP7M4

5.17.29 INV_1M2_1LP7

5.17.30 INV_1_1LP7

5.17.31 INV_2M16_1P8M8

5.17.32 INV_2M16_2LP7M8

5.17.33 INV_2M2_1LP7

5.17.34 INV_2M2_1P8

5.17.35 INV_2M2_2LP7

5.17.36 INV_2M4_1P8M2

5.17.37 INV_2M4_2LP7M2

5.17.38 INV_2M8_2LP7M4

5.17.39 INV_2_1LP6

5.17.40 INV_2_1LP7

5.17.41 INV_2_1LP8

5.17.42 INV_2_1LP7_M2

5.17.43 INV_2_1_LP7

5.17.44 INV_2_P9

5.17.45 INV_3M2_3_L1P2

5.17.46 INV_4M2_4LP7

5.17.47 INV_4_2LP7

5.17.48 INV_5L1P5_4L2

5.17.49 INV_P7_1_LP7

5.17.50 MUX21N_2M2_1P8

5.17.51 MUX21_2M2_1P8

5.17.52 MUX21_2M2_2LP7

5.17.53 NAND2B1_2_2LP7

5.17.54 NAND2_2_1P8

5.17.55 NAND2_2_2LP7

5.17.56 NAND2_2_2LP7_M2

5.17.57 NOR2_2M2_1P2

5.17.58 NOR2_2M2_1P5LP7_X1

5.17.59 NOR2_2M2_1P5LP7

5.17.60 NOR2_2M4_1P8

5.17.61 NOR3_2M2_1P2

5.17.62 NOR3_2P5M2_1P5LP7

5.17.63 SMITINV_2_1LP7

5.17.64 SMITINV_2_1LP7_X1

5.17.65 OAI21_2M2_2LP7

5.17.66 OAI21_2M2_1P8

5.17.67 OR2_2M2_2LP7

5.17.68 OR2_2M3_1P8

5.17.69 OR3B3_2M2_2LP7

5.17.70 OR3_2M2_1P8

5.17.71 OR3_2M2_2LP7

5.17.72 RS_LATCH_2M2_1P5LP7

5.17.73 RS_LATCH_2_2LP7

5.17.74 RS_LATCH_2_1P8

5.17.75 RS_LATCH_2_2LP7_X1

5.17.76 RS_LATCH_5L1P5_10L2

5.17.77 SMITBUF_3P2L1P2M2_2P5L1

5.17.78 TIEHI_2_1LP7

5.17.79 TIELO_2_P9

5.17.80 XNOR2_2M2_2LP7

5.17.81 XOR2_2M2_1P8

5.18 VSUB_CLAMP